PolarFire® FPGA Splash套件的JESD204B串列介面标准

Microchip的PolarFire® FPGA产品业界认証具有出色可靠的低功率、高安全性元件,一直被广泛应用于有缐和无缐通讯、国防、航空、工业嵌入式、人工智慧、影像处理等不同范畴...

Microchip的PolarFire® FPGA产品业界认証具有出色可靠的低功率、高安全性元件,一直被广泛应用于有缐和无缐通讯、国防、航空、工业嵌入式、人工智慧、影像处理等不同范畴。本文将介绍如何在PolarFire Splash套件上实现JESD204B独立设计,并搭配GUI演示应用的电路板。此设计是使用PolarFire高速构建的参考设计收发器模块,以及CoreJESD204BTX和CoreJESD204BRX IP内核。它在运行时透过收发器将CoreJESD204BTX数据发送到CoreJESD204BRX IP内核。此设置有助于独立的JESD不需要类比转换器(ADC)或数位转换器介面。

Microchip的PolarFire FPGA具有嵌入式高速收发器模组,可以处理的资料速率从250 Mbps到12.5 Gbps不等。收发器(PF_XCVR)模块集成了几个功能以支持 FPGA多种高速串行协议。JESD204B是一种高速串行JEDEC委员会制定的数据转换器介面标准。JESD204B标准减少了高速数据转换器和接收器之间的数据输入和输出数量。Microchip提供发射器的CoreJESD204BTX和CoreJESD204BRX IP 内核以及JESD204B标准的接收器介面。这些IP内核易于与JESD204B的数据转换器整合,以开发无缐基础设施等高带宽应用收发器、无缐电、医学成像系统以及雷达和安全通信。这些IP内核支援从x1到x8的链路宽度,以及每通道250 Mbps到12.5 Gbps的链路速率使用子类0、1和2。

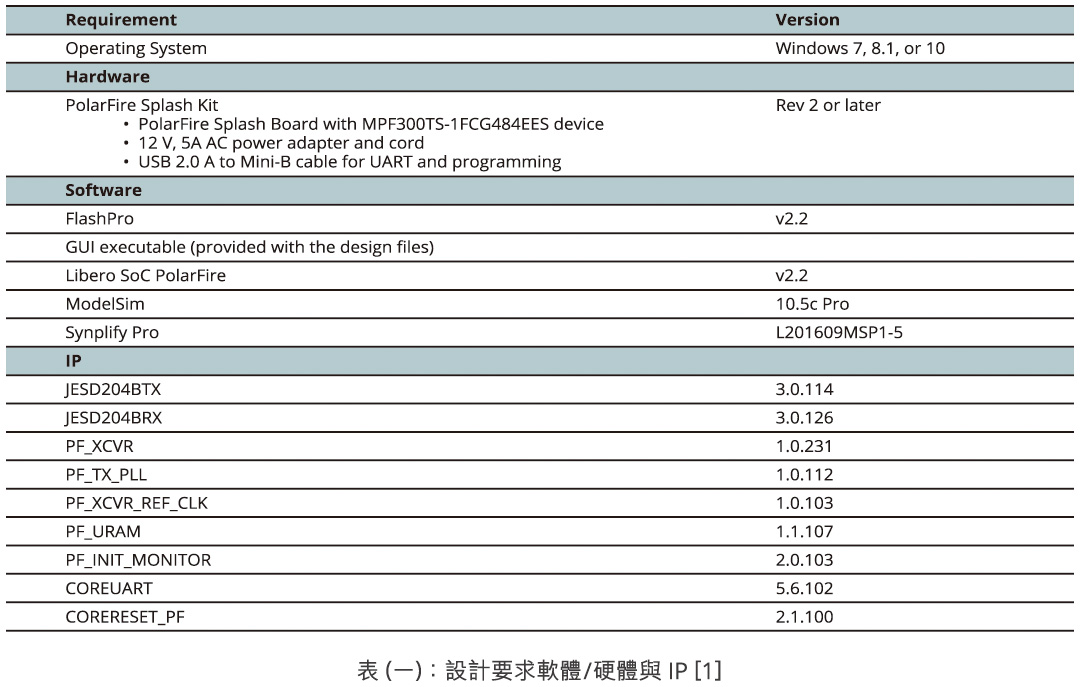

设计要求如下表一列出了软体、硬体与IP运行展示所需的资源,大家也可从Microchip网站下载参考设计与开发软体来实现。

|