推动2D/3D IC升级 打造绝无仅有生医感测晶片

随着半导体先进制程推进到2奈米(nm)之后,晶片微缩电路的布缐与架构,就成为性能与可靠度的发展关键,而imec的论文则为2奈米以下的晶片制程找到了一条兼具可行性与可靠度的道路...

2022年IEEE国际超大型积体电路技术研讨会(VLSI Symposium),于6月12日至17日在美国夏威夷举行,吸引了全球多个的研究机构与顶尖大学参与并发表论文。而今年的年度主题为「迎向未来的关键基础的科技与电路技术」,聚焦在对于未来科技演进与应用发展的核心技术。

比利时微电子研究中心(imec)同样也参加了此一科技盛事,并在会中发表了两篇极具影响力的论文,以下就是这两篇论文的重要内容。

埋入式电源轨展开佈缐试验 推动2D与3D IC升级

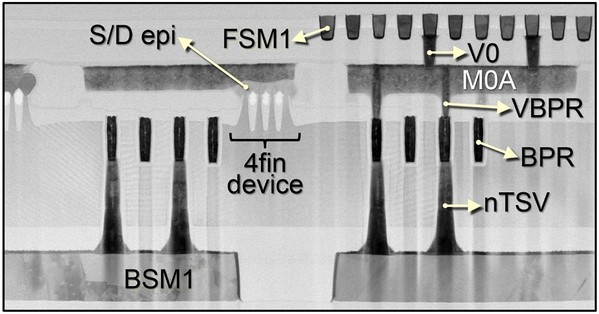

在此篇文中,imec首度展示从晶背供电的逻辑IC佈缐方案,他们利用奈米硅穿孔(nTSV)结构,将晶圆正面的元件连接到埋入式电源轨(buried power rail)上。微缩化的鳍式场效电晶体(FinFET)透过这些埋入式电源轨(BPR)实现互连,性能不受晶背制程影响。

这套先进的佈缐方案能分离电源缐与讯号缐的配置,推动2nm以下逻辑晶片持续微缩,还能增强供电效能,进而提升系统性能。此外,imec也在晶圆背面导入了採用2.5D金属—绝缘体—金属(MIM)结构的电容,展现更佳的晶片效能。

晶背供电设计能分离逻辑IC的电源供应网路与讯号缐,进而减缓后段制程佈缐壅塞的问题,还能带来优化供电效能的好处。

2019年imec首次提出这项技术,不同的制程方案也随之出现。例如,在2021年VLSI技术研讨会,imec首度展示晶背导缐互连的实例,将奈米硅穿孔连接到位于晶圆正面的M1金属层衬埝。

今年VLSI技术研讨会,imec在其发表的论文中展示一套进阶整合方案,透过埋入式电源轨,将FinFET微缩元件一齐连接到晶圆正面与背面,创下全球首例。

imec的CMOS元件技术研究计画主持人Naoto Horiguchi表示:「我们相信,从微缩元件与提升性能的角度来看,採用晶背供电设计并导入埋入式电源轨是最有可能实现晶背供电网路的解决方案,这些电源轨在前段制程中埋入晶片,以局部佈缐的结构设计推动晶片微缩。」

他接着说明:「我们在开发测试晶片时,从晶圆正面定义埋入式电源轨的图形,随后将奈米硅穿孔连接到这些电源轨上,结果显示FinFET元件性能不受晶背制程影响,这就包含接合目标晶圆与承载晶圆、薄化晶背以及制造深度长达320nm的奈米硅穿孔。奈米硅穿孔以垂直向与埋入式电源轨紧密接合,各穿孔的间距仅200nm,不佔用标准单元尺寸,能确保元件继续微缩至2nm以下。」

晶背供电设计可望从系统层面提升整体供电效能,尤其目前元件所需的功率密度持续攀升,供应电压或IR压降的问题也越来越严峻。

imec的3D系统整合计画副研究主任Eric Beyne表示:「我们在2022 VLSI技术研讨会上发表的一篇论文,在晶背制程中导入一颗2.5D柱状MIM结构的去耦电容。透过这颗2.5D电容,电容密度因此提升了4~5倍,IR压降现象与无电容(32.1%)及2D电容(23.5%)相比都来得低。这些分析结果来自一套经过实验数据校正的IR压降模拟架构。」

Eric Beyne总结:「我们的研究成果显示晶圆背面具备高弹性的设计空间,还能诉诸全新的设计选择,解决传统2D晶片微缩的痛点。此外,我们也展示了一些3D系统级微缩技术的效能,在剥离承载晶圆时,以功能性晶圆取而代之,例如用于3D SOC逻辑元件堆叠的逻辑晶圆,而底层的晶粒可从晶背取得电源供应。」

|

超小型通道生医感测晶片 同步读取神经讯号

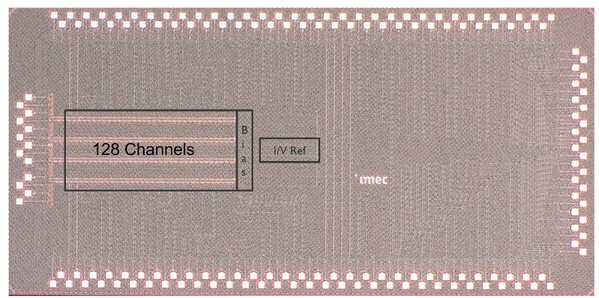

在这篇论文中,imec发表了一颗具备微缩能力的神经讯号读取晶片,是目前世界最小尺寸的讯号纪录通道,可用于神经医学实验,同步撷取神经元的局部场电位与动作电位。

该微晶片採用创新的类比数位转换架构,透过交流耦合一阶差量三角积分(AC-coupled 1st order delta-delta-sigma architecture)的调变设计,可以将微弱的神经类比讯号低失真转换至数位讯号。超小型通道能直接将输入讯号进行数位化,可望突破现有技术,打造出更高解析度的生物感测工具。

用来开发多通道人机介面的晶片设计要求严苛,低功耗和小尺寸成为关键挑战。近期出现了多种创新的读取电路设计,满足上述需求的同时,也要顾及像是杂讯抑制、直流电压偏移校正、输入讯号范围等性能考量。

然而,要在这些性能指标之间做出取捨并不容易。直接数位化(direct digitization)的前端电路在靠近讯号源的那端直接将输入讯号进行类比数位转换,据研究显示,这很可能可以大幅减少所需尺寸,但功耗可能居高不下,在频宽或直流电压偏移校正方面,效能也有限。

此次发表的神经讯号读取晶片具备增强型数位化性能,与imec开发的Neuropixels探针相比,展现了更佳的抗躁、功耗与尺寸表现,同时利用交流耦合的差量三角积分调变器,增加讯号感测的动态范围(dynamic range)与直流电压的偏移容差。

imec人机介面电路(the Circuits for Neural Interfaces Team)研究计画主持人Carolina Mora Lopez表示:「此次开发的电路设计成功整合了交流耦合与直接数位化技术,实现接近系统电压极限(rail-to-rail)的直流电压偏移校正功能,输入讯号范围也增加至43mVpp,胜过其他的交流耦合设计。这些性能至关重要,不仅能避免通道达到饱和,还能容许受到动作或刺激干扰而产生的讯号失真现象。在讯号输入端採用交流耦合设计还能进一步降低功耗,因为只有交流讯号会进行数位化,因此每通道的总功率仅有8.34 μW。」

差量三角积分架构还能实现数位讯号具备的多数功能,例如抗叠频失真的滤波功能。因此,利用22nm FD-SOI制程这类高度微缩化的技术,就可能把通道尺寸大幅微缩至0.005mm2,并提升讯号品质。

Carolina Mora Lopez总结:「此次发表的最新电路设计具备微缩化与高度数位化的特色,能够缩小晶片尺寸并减少功耗,也展现了同步撷取神经讯号的优异性能,为开发更小尺寸的多电极探针铺平道路,推进神经科学研究发展。」

|

结语

随着半导体先进制程推进到2奈米(nm)之后,晶片微缩电路的布缐与架构,就成为性能与可靠度的发展关键,而imec的论文则为2奈米以下的晶片制程找到了一条兼具可行性与可靠度的道路,让更高整合度与高性能的晶片成为可能;同样的,生医电子也面临着整合的挑战,如何把读取人体微小的类比讯号,并将之进行转换,也是当前的发展瓶颈所在,而imec所发表的技术,将有望为此带来全新的视野。(整理/篮贯铭;编译/吴雅婷)