以模型为基础的设计方式改善IC开发效率

以模型为基础的设计开发,在Simulink建立模型并模拟混和讯号IC设计、受控体和微机电系统(MEMS),本文展示马达和感测器的范例。...

以模型为基础的设计开发,在Simulink建立模型并模拟混和讯号IC设计、受控体和微机电系统(MEMS),可让产品团队在进行电路层级的设计之前,先经过高层级的设计规格验证,藉此能够有效提升整体设计品质。本文展示马达和感测器的范例。

为了应付不断提高的竞争压力,积体电路(integrated circuit;IC)制造商即便面对设计复杂度以及客户对于品质和产品性能的要求均提升的情况,还是必须盡可能地缩短交货时程。许多制造商发现让团队执行以文件为基础的规格验证,并且传统的设计途径在最终生产版本确认之前,必须经过多次制作产品原型,这样的开发速度已很难跟上现今的产业节奏。

在ROHM,把以模型为基础的设计整合加入马达控制应用、感测器应用、电源系统等IC开发流程。在Simulink建立模型并模拟混和讯号IC设计、受控体、和微机电系统(microelectromechanical systems;MEMS),可让产品团队在进行电路层级的设计之前,先经过高层级的设计规格验证。这样的方式减少重复工作、开发时间、以及原型的数量,同时也提升整体设计品质。

举例来说,在Simulink建立及验证的模型自动产生Verilog程式码,将可使花费在验证上的时间从一个月缩短为几天。除了开发效率之外,设计品质也获得改善,甚至是可以让执行阶段错误的数量减少为零。

透过以模型为基础的设计,我们可以建立产品的原型?且该产品原型经过了模型层级的规格验证,并确认电路层级的功能和特性符合设计规格?也只需要建立一次的产品原型,便直接从原型进入到量产阶段,而不需要让建立原型的步骤反覆进行三到四次。

以模型为基础的马达控制IC设计

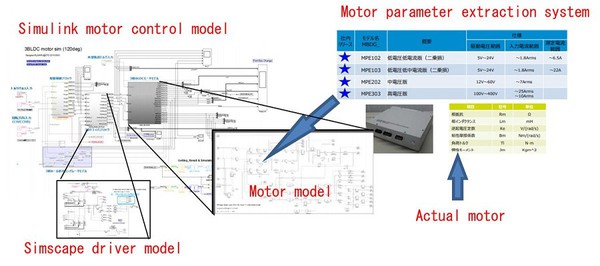

在开发马达控制应用的IC时,我们的团队从建立被控制的马达模型来开始设计流程。在Simulink使用运动方程式和电压方程式来建立马达的机构与电气特性的模型,接着使用MATLAB来依据马达实际的量测值进行模型参数的拟合。按团队所设计的马达模型,也可以纳入因电感式感测控制造成的磁饱和(magnetic saturation)效应以及轴心错位(shaft misalignment)造成的颤动和晃动。作为受控体模型的一部分,将透过Simscape建立的马达驱动器电晶体的模型加进来(图1)。这个驱动器模型能够分析瞬变的特性,例如脉冲宽度调变开始时因为马达缐圈内的寄生电容(parasitic capacitance)造成的电流震盪。

|

在Simulink建立了马达的控制器模型,接着执行加入控制器和受控体的系统层级模拟,检查设计当中控制函式的速度、位置及上升。在透过此方法验证控制器设计之后,使用Fixed-Point Designer(定点设计工具箱)将控制演算法转换为定点。接着利用HDL Coder(硬体描述语言转码器)从模型产生可合成的Verilog RTL程式码,不但加快实现的速度,并且消除先前以手动编写程式码时所面临的编程错误风险。

藉由DPI-C模型生成开发MEMS装置

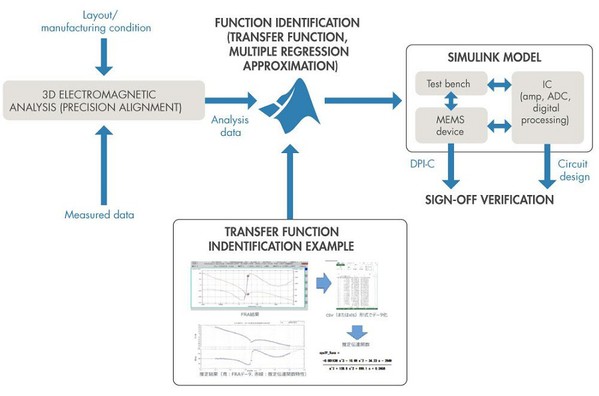

对于牵涉到MEMS感测器及和感测器IC相关的专案,我们採用的开发流程与马达控制IC使用的开发流程类似。不过,这里不以执行测试来进行马达的特性化,而是使用3D电磁分析和结构分析来进行MEMS装置的特性化,接着将透过这项流程所定义的参数,拟合至装置的Simulink模型。或者在MATLAB执行转换函式辨识和多重迴归的近似值,接着将转换函式作为装置的一个模型来使用。

我们建立一个感测器IC的Simulink模型,与马达控制器模型相似,可被当作设计的可执行规格。透过Simulink的系统层级模拟,可以在Cadence Virtuoso平台上调整设计之前,便及早进行规格的验证。

在MEMS设计工作流程上,还可以执行不在马达工作流程之中的额外验证步骤。我们特別使用HDL Verifier(HDL设计验证工具)搭配Embedded Coder(嵌入式程式码转码器)从Simulink MEMS装置模型产生一个SystemVerilog DPI-C模型(图2)。

|

接下来,在Cadence环境里面使用SystemVerilog模型来完整检验我们的IC设计(包括放大器、类比数位转换器、数位处理逻辑),并且一面在sign-off验证之前,持续地使设计精进完善。这项技巧不只提高了开发效率,也因为我们在Simulink及Cadence Virtuoso均通过一致的设计验证,而有助于确保设计品质。

以FPGA迴圈供客户评估

我们的许多客户发现,能够对开发当中的ROHM产品进行评估的这项能力,可为自家的开发过程带来重要的帮助。对于这些客户,我们使用HDL Coder从Simulink IC模型产生HDL程式码,并且将模型部署至FPGA评估板。这些客户便可以使用板子来评估他们的硬体设计。并且可以使用HDL Verifier来搭配其系统层级Simulink模型执行FPGA迴圈模拟,以进行瞬变分析和设计优化。这两种方法让我们的机密IP受到保护,因为分享出去的只有FPGA上的实现,而不是我们的原始设计资产。

创立以模型为基础的设计群组

为了帮助ROHM的产品团队导入以模型为基础的设计方式,我们发起一个以模型为基础的设计群组,由具备丰富设计经验的工程师团队组成。这个群组开发可让其他团队更轻松地在Simulink执行建模、模拟的资产,做为由上而下的IC设计工作流程的一部分。资产包含模型样板、文件、工具(例如参数撷取的工具),以及马达模型、MEMS模型、SystemVerilog DPI-C生成的技术指南。

这个群组也分享建模技巧、进行内部的简报和教育训练来帮助团队快速上手。群组一开始是以日本当地的ROHM团队作为目标对象,现在则协助ROHM的海外设计中心筹建擅长于以模型为基础的设计专案的团队。

许多ROHM团队已做好採用以模型为基础的设计的准备,虽然有少数仍然因为尚未建立好他们所属领域的以模型为基础的设计环境而有些抗拒。针对后者,以模型为基础的设计群组会多花时间展现採取该途径的好处,以及其他已採用团队体认到的优势。更近期,我们也设置了使用Simulink来开发感测器IC和马达IC的工作群组。ROHM工程师加入这些群组来分享技术资讯和了解更多和许多群组相关的主题,包含如何在Simscape建立MOSFET驱动器模型、如何建立高精确度的MEMS模型,以及如何辨识现有电路的频率响应。

延伸使用以模型为基础的设计

在我们所属的单位之中,使用以模型为基础的设计的团队数量呈现稳定成长。此外,开始看到以模型为基础的设计被运用在公司的各个事业部,包含负责开发和生产碳化硅(silicon carbide;SiC)和绝缘闸双极电晶体(insulated-gate bipolar transistor;IGBT)产品的团队。最近也从汽车产业客户看到更多以模型为基础的设计的需求。ROHM现在处于符合这些需求的绝佳位置。

(本文由钛思科技提供;作者Kyoji Marumoto、Hiroshi Nishide任职于ROHM公司)