超越5G时代的射频前端模组

透过整合深宽比捕捉(ART)技术与奈米嵴型工程,爱美科成功在300mm硅基板上成长出砷化鎵或磷化铟鎵的异质接面双极电晶体,实现5G毫米波频段的功率放大应用。...

透过整合深宽比捕捉(ART)技术与奈米嵴型工程(nano-ridge engineering),爱美科成功在300mm硅基板上成长出砷化鎵(GaAs)或磷化铟鎵(InGaP)的异质接面双极电晶体(HBT),实现5G毫米波频段的功率放大应用。

前四代的行动通讯技术在传输频率方面的变革,一向呈现逐步演进,而非革命性的。操作频率从仅不到十亿赫(GHz),跃升至好几十亿赫,而频宽也从几十千赫(kHz)扩展至几十百万赫(MHz)。

从这些传输特性来看,第五代行动通讯技术(5G)可说是脱离过往所有技术的激进变革。5G的部分传输工作仍会使用一些GHz频率—也就是sub-6 GHz频段,但除此之外,它还使用了毫米波频段,也因此,现行的网路频段需要处理相关的频宽限制问题。

|

使用毫米波的缺点之一,例如以28GHz与39GHz为主的频段,在于讯号功率会出现明显衰减。为了解决这项痛点,5G网路开始出现部署小型基地站的需求,还需开发全新的行动装置设计,使得元件的前端设计变得更加复杂。

以砷化鎵(GaAs)或磷化鎵铟(InGaP)制成的异质接面双极电晶体(HBT),是目前行动装置的关键元件,其成长于造价不菲的GaAs基板上。这类电晶体被用来制造功率放大器,该元件特色是具备多个独立模组,不同模组处理不同频段。

随着5G网路开始支援毫米波频段,HBT元件的射频性能势必要维持水准,甚至进一步提升,同时还要降低成本、增加电路设计弹性、减少功率耗损与元件尺寸。不幸的是,目前的商用技术还在努力开发出优良的射频前端模组,满足上述所有需求,因此改用创新材料与元件架构,成为时势所需。

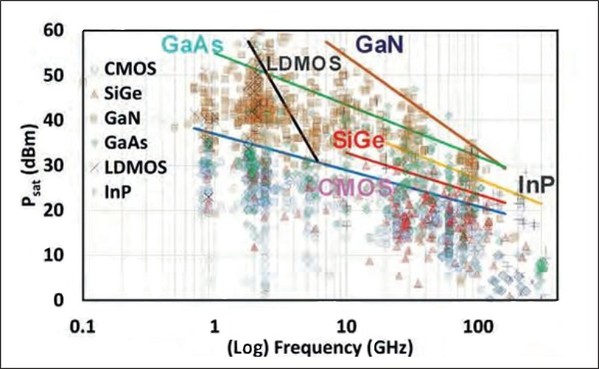

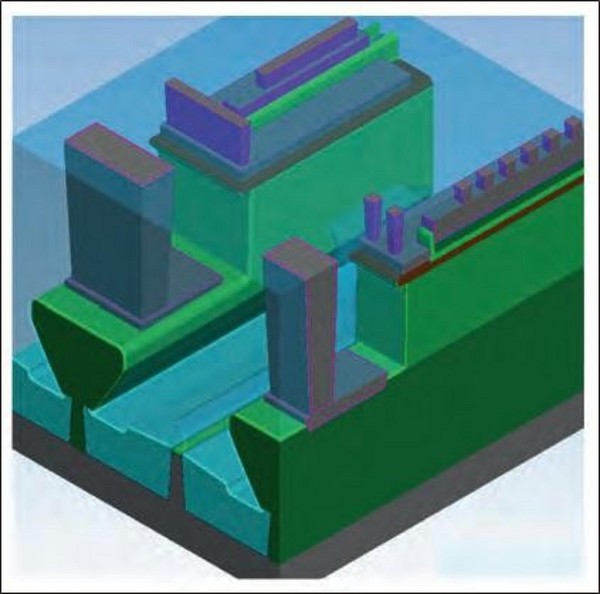

爱美科已经开发出异质三五族CMOS技术,能够满足毫米波射频应用的小尺寸、低成本需求。这项技术在高频状态下操控三五族元件系统的功率负载(图二)以及缐性度,并利用先进的CMOS后段制程来制造复杂的控制电路。

此外,多亏了共整合(co-integration)技术,这项技术还有可能进一步改善整体电路的能耗效率,实现可供量产的高能耗效率、低成本的毫米波技术。

|

要将像是GaAs的三五族材料与硅材整合,其中一项的最大挑战,就是严重的晶格不匹配。在晶格不匹配的硅基板上进行磊晶成长会产生缺陷—多半是穿隧差排(threading dislocation)。这些缺陷会导致不被乐见的漏电流,折损元件性能。

有些研究团队在硅基板与元件之间导入一层应力松弛的缓冲层,持续努力降低这些缺陷密度。但是增加元件层就会加诸庞大的成本。这些增设的元件层以硅锗(SiGe)、锗或三五族变晶堆叠制成,且堆叠厚度需达至少10μm,才能有效将缺陷密度降至可接受的数值。

事实是,不论要用什么方法来开发CMOS三五族技术,为了控制元件的复杂度与制造成本,势必要採用标准硅基板。

深宽比捕捉技术

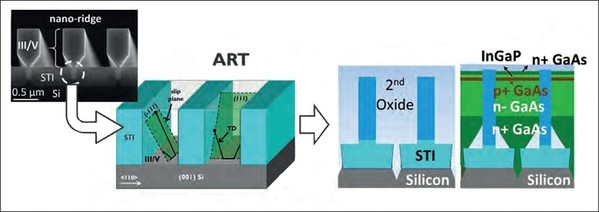

爱美科的解决方法是结合深宽比捕捉技术与奈米嵴型工程,前者将缺陷侷限在窄沟底部,后者可实现零缺陷且可增加产量的三五族元件制造(图三)。随后採用完全相容于CMOS的制程来进一步处理奈米嵴结构,制出最终的元件,并实现与硅基CMOS元件的共整合。

|

这项作法的优势之一是,能在不需成长厚缓冲层或使用昂贵基板的情况下,将硅基版与三五族材料进行整合。况且爱美科还能善用其以300mm晶圆制造三五族元件(III-V-on-300 mm)的专业技术—当初开发是为了要持续微缩CMOS技术和研究硅基CMOS元件。

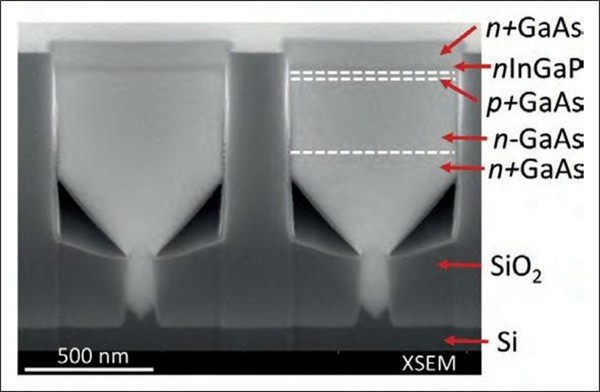

为了制造奈米嵴,爱美科将三五族材料成长于300mm的(001)硅晶圆上,採用双层氧化层的结构(图四)。第一层二氧化硅(SiO2)层是400nm的浅沟隔离(shallow trench isolation;STI)模板,其特色在于80nm宽的窄沟图形,且底部有{111}硅晶向的V型槽,间隙为800nm。

|

在这之上,爱美科加了第二层氧化层,厚度为1000nm,成长出600nm宽的沟槽,位于下层窄沟的中间。

之后,运用选区成长(selective-area growth)技术,爱美科将三五族材料沉积在窄沟内。三五族材料与硅材之间的严重晶格不匹配会产生缺陷,但这些缺陷,因为高深宽比的结构,会被侷限在沟槽底部。这就确保了窄沟外成长的材料能免除穿隧差排的缺陷。

接下来是进行奈米嵴型工程,藉由拓宽奈米嵴来维持(001)长晶面,制出平坦的接面。倘若奈米嵴型工程能成长出独立式的元件架构,会导致大的盒型图形。为了避免这个现象,爱美科加了第二层氧化层模板。一旦奈米嵴碰到第二层氧化层,就会减少元件主动区的侧壁沉积。

爱美科在低压的金属有机化学气相沉积(MOCVD)腔体中,在300mm硅晶圆上成长出这些三五族材料,由于反应物来源是三五族材料,因此使用传统的液相前驱物。另加入四溴化碳(carbon tetrabromide)与硅烷(silane)进行掺杂。

要注意的是,奈米嵴型工程不仅能制造传统三五族上硅元件的盒形成长(box-like growth),还能透过仔细调整成长条件来制出不同图形,进而能以奈米等级准确操控奈米嵴的轮廓。

缺陷的特徵分析

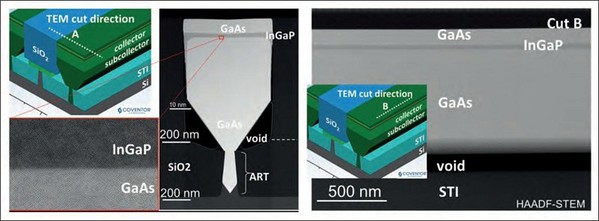

为了评估这套方法的有效性,爱美科进一步分析奈米嵴内的缺陷密度。而检视材料最常用的技术之一,就是穿透式电子显微镜(TEM)。爱美科使用的是TEM中的高角度环型暗场扫描(high-angle annular dark-field scanning),它能揭露沟槽内的缺陷。结果显示,爱美科的三五族堆叠中并沒有错合差排(misfit dislocation)(图五、图六)。

虽然传统的TEM能提供更准确的缺陷侦测,但其扫瞄范围很小,若要以此取得可靠的缺陷密度,过程会相当繁琐。

|

另一项常用来检视材料的技术是电子通道对比影像(electron channeling contrast imaging),它能相对迅速地产生具备统计相关意义的资料集。藉此,爱美科发现,在GaAs奈米嵴表面的穿隧差排密度低于3x106 cm2。由于缺陷密度的数值受限于扫描区的大小,爱美科预计,GaAs奈米嵴内的穿隧差排密度,实际上还会比上述数值更低。

基于这项研究结果,可以知道爱美科开发的奈米嵴,穿隧差排密度低,足以防止元件受到重大的负面影响。

晶格常数不匹配的磊晶系统,也可能会因为面缺陷(planar defect)而佈满孔洞。爱美科的方法,是将这类缺陷捕捉在与侧壁平行的{111}晶面上,但是当面缺陷与侧壁垂直时,面缺陷有可能会落入元件堆叠内。这个情况下,密度可能介于0.14μm-1~0.45μm-1。庆幸的是,由于面缺陷不包含开放的晶体键(open crystal bond)或应变场,因此对元件性能的影响比差排缺陷小。

300mm硅上HBT元件

爱美科利用其零缺陷硅上三五族元件层的成长技术,已经展出以单晶整合于300mm标准硅基板上的GaAs/ InGaP材料HBT元件,成功在超越5G时代的应用中,为基于InGaAs的元件提供技术跳板。

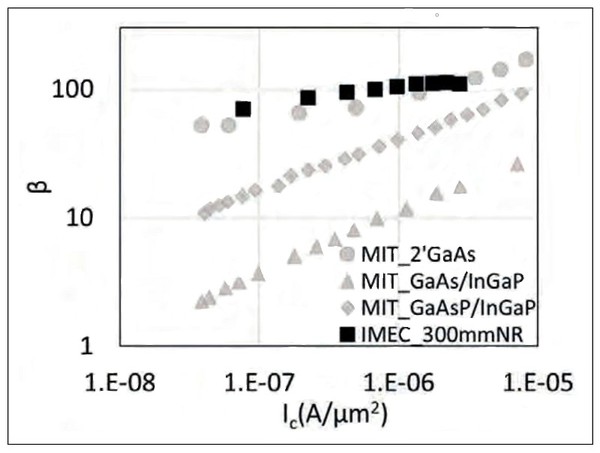

这项技术取得重大进展的基础,在于採用n-InGaP/p-GaAs/n-GaAs架构的一组堆叠,其展现了HBT的元件特性。该堆叠的射极-基极二极体,以及基极-集极二极体,理想因子分別约为1.2和1.4,显现了在接面与成长材料方面的优异品质。此外,其DC电流增益可高于110,集极-基极的崩溃电压为10V,也能证明这个架构具备优良的材料品质。

|

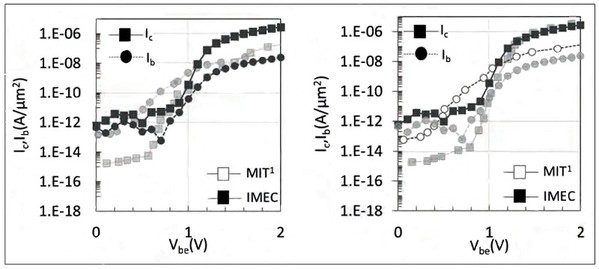

为了衡量元件的标准,爱美科针对元件转换特性,比较这款HBT元件与採用类似设计的其他HBT元件;参考元件在2吋GaAs基板上制造,其应力松弛且厚的缓冲层,具备与爱美科HBT元件相似的缺陷密度(图七)。结果令人振奋,爱美科元件的性能胜过具备厚缓冲层的参考元件,且爱美科元件的性能特点,与成长于2吋高品质GaAs基板的元件极为相似(图八)。

这项研究结果与爱美科所言相符,其提出的奈米嵴型工程,以300m硅基板制造,能充分提供所需的材料品质—也就是说,不论是应力松弛且厚的缓冲层,或昂贵的基板,其实都不需要。

|

爱美科的硅上三五族元件成功取得了优异的研究成果,因此对这项技术抱持了高度期待。这项技术的优势之一,展现在三五族材料与CMOS硅基制程的整合能力,进而实现5G与毫米波应用。它可以在300mm硅基板上成长出採用InGaAs材料的HBT元件,部署在5G世代之后的射频应用中。

爱美科的异质三五族CMOS技术,从初期的元件性能表现,逐渐改良至现今堪比高品质GaAs基板制成的元件性能。爱美科将持续开发奈米嵴型工程技术,充分发挥其潜力。

(本文由爱美科授权刊登;作者Amhitosh Vais为爱美科研究员/编译:吴雅婷)

**刊头图(source:imec-int.com)