模拟器件公司(Analog) AD9361BBCZ 器件介绍_规格参数_引脚图_应用领域

AD9361BBCZ 是一款高性能、高集成度射频 (RF) 敏捷收发器,设计用于 3G 和 4G 基站应用。

AD9361BBCZ 器件介绍

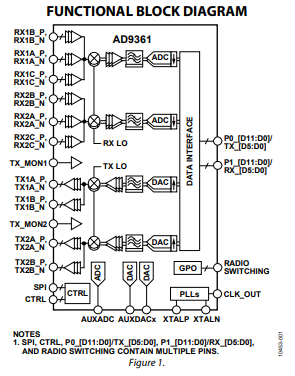

模拟器件公司 (Analog) 的 AD9361BBCZ 是一款高性能、高集成度的射频收发器芯片。设计用于3G和4G基站。AD9361BBCZ 集成了宽带能力和可编程性,使其适用于各种收发器应用。接收器LO工作频率为70 MHz至6.0 GHz,发射器LO工作频率为47 MHz至6.0 GHz,覆盖大多数许可和非许可频段,并支持小于200 kHz至56 MHz的信道带宽。AD9361BBCZ有两个独立的直接转换接收器,每个接收器具有一流的噪声系数和线性度,并包括独立的AGC、直流偏移校正、正交校正和数字滤波功能。此外,AD9361BBCZ具有可灵活手动增益模式和每个通道有两个高动态范围ADC,发射机采用直接转换架构,可实现高调制精度和超低噪声。AD9361BBCZ还具有完全集成的PLL,可为所有接收和发射通道提供低功耗小数N频率合成,并且所有VCO和环路滤波器元件均已集成。该器件可以直接由1.3 V稳压器供电,并通过一个标准4线串行端口和四个实时输入/输出控制引脚进行控制。

AD9361BBCZ 规格参数

- 工作温度: -40摄氏度~85摄氏度

- 安装类别: 贴片

- 种类: 仅TxRx

- 制造厂商: 模拟器件公司(Analog)

- 协议: LTE

- 电源电压: 1.267伏 - 1.33伏

- 封装: 144-LFBGA,CSPBGA

- 收发器: 2 × 2

- 接收频率: 70MHz ~ 6GHz

- 发送频段:47MHz ~ 6GHz

- 信道带宽: <200 kHz 至 56 MHz

- 发射机噪声: ≤-157 dBm/Hz

- 接收状态电流: 175毫安 ~ 445毫安

- 发送状态电流: 240毫安 ~ 820毫安

- 封装: BGA-144

- 封装尺寸: 10mm x 10mm

- 输出功率: 8dBm

- 数字接口: CMOS/LVDS

- RoHS标准: 符合

- 含铅标准: 无铅

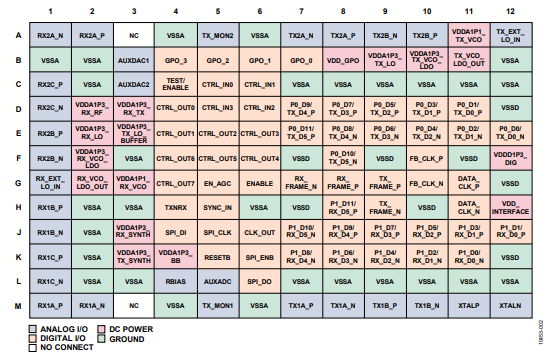

AD9361BBCZ 引脚定义

AD9361BBCZ 引脚图

| 引脚 | 类型 | 助记符 | 描述 |

|---|---|---|---|

| A1, A2 | I | RX2A_N, RX2A_P | 接收通道 2 差分输入 A。或者,每个引脚可用作单端输入或组合成一对差分输入。将未使用的引脚接地。 |

| A3, M3 | NC | NC | 无连接。请勿连接至这些引脚。 |

| A4, A6, B1, B2, B12, C2, C7 to C12, F3, H2, H3, H6, J2, K2, L2, L3, L7 to L12, M4, M6 | I | VSSA | 模拟接地。将这些引脚直接与印刷电路板上的 VSSD 数字地线相连(一个接地平面)。 |

| A5 | I | TX_MON2 | 传输通道 2 电源监控器输入。如果该引脚未使用,则将其接地。 |

| A7, A8 | O | TX2A_N, TX2A_P | 传输通道 2 差分输出 A。将未使用的引脚绑至 1.3 V。 |

| A9, A10 | O | TX2B_N, TX2B_P | 将未使用的引脚绑至 1.3 V。 |

| A11 | I | VDDA1P1_TX_VCO | 发射 VCO 电源输入。连接至 B11。 |

| A12 | I | TX_EXT_LO_IN | 外部发射 LO 输入。如果该引脚未使用,则将其接地。 |

| B3 | O | AUXDAC1 | 辅助 DAC 1 输出。 |

| B4 to B7 | O | GPO_3 to GPO_0 | 3.3 V 通用输出。 |

| B8 | I | VDD_GPO | 2.5 V 至 3.3 V 电源用于 AUXDAC 和通用输出引脚。不使用 VDD_GPO 电源时,该电源必须设置为 1.3 V。 |

| B9 | I | VDDA1P3_TX_LO | 传输 LO 1.3 V 电源输入。 |

| B10 | I | VDDA1P3_TX_VCO_LDO | 传输 VCO LDO 1.3 V 电源输入。连接至 B9。 |

| B11 | O | TX_VCO_LDO_OUT | 发射 VCO LDO 输出。连接至 A11 和一个 1 µF 旁路电容器,该电容器与一个 1 Ω 电阻器串联接地。 |

| C1, D1 | I | RX2C_P, RX2C_N | 每个引脚可用作单端输入或组合成一对差分输入。这些输入在 3 GHz 以上时性能会下降。将未使用的引脚接地。 |

| C3 | O | AUXDAC2 | 辅助 DAC 2 输出。 |

| C4 | I | TEST/ENABLE | 测试输入。将此引脚接地,以保证正常工作。 |

| C5, C6, D6, D5 | I | CTRL_IN0 to CTRL_IN3 | 控制输入。用于手动 RX 增益和 TX 衰减控制。 |

| D2 | I | VDDA1P3_RX_RF | 接收器 1.3 V 电源输入。连接至 D3。 |

| D3 | I | VDDA1P3_RX_TX | 1.3 V 电源输入。 |

| D4, E4 to E6, F4 to F6, G4 | O | CTRL_OUT0, CTRL_OUT1 to CTRL_OUT3, CTRL_OUT6 to CTRL_OUT4, CTRL_OUT7 | 控制输出。这些引脚是多用途输出,具有可编程功能。 |

| D7 | I/O | P0_D9/TX_D4_P | 数字数据端口 P0/传输差分输入总线。这是一个双功能引脚。 作为 P0_D9,它是 12 位双向并行 CMOS 电平数据端口 0 的一部分。此外,该引脚(TX_D4_P)还可作为具有内部 LVDS 终端的 LVDS 6 位发送差分输入总线的一部分。 |

| D8 | I/O | P0_D7/TX_D3_P | 数字数据端口 P0/发送差分输入总线。这是一个双功能引脚。 作为 P0_D7,它是 12 位双向并行 CMOS 电平数据端口 0 的一部分。此外,该引脚(TX_D3_P)还可作为具有内部 LVDS 终端的 LVDS 6 位发送差分输入总线的一部分。 |

| D9 | I/O | P0_D5/TX_D2_P | 数字数据端口 P0/发送差分输入总线。这是一个双功能引脚。 作为 P0_D5,它是 12 位双向并行 CMOS 电平数据端口 0 的一部分。此外,该引脚(TX_D2_P)还可作为具有内部 LVDS 终端的 LVDS 6 位发送差分输入总线的一部分。 |

| D10 | I/O | P0_D3/TX_D1_P | 数字数据端口 P0/发送差分输入总线。这是一个双功能引脚。 作为 P0_D3,它是 12 位双向并行 CMOS 电平数据端口 0 的一部分。此外,该引脚(TX_D1_P)还可作为具有内部 LVDS 终端的 LVDS 6 位发送差分输入总线的一部分。 |

| ......省略 | |||

以上是部分引脚定义,完整定义请参阅芯片手册:

https://www.analog.com/media/en/technical-documentation/data-sheets/AD9361.pdf

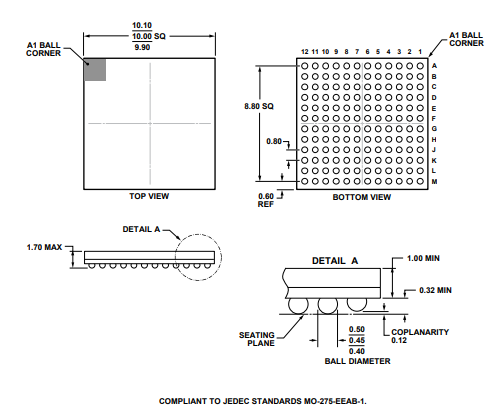

AD9361BBCZ 封装

AD9361BBCZ 采用 144-CSPBGA 工艺封装,尺寸为 10mm x 10mm

AD9361BBCZ 封装图

工作原理

功能框图

主要应用领域

AD9361BBCZ 丰富的内置模块、优秀的RF性能与可编程性,十分适合以下场景:

- 点对点通信系统:AD9361BBCZ提供高性能、低功耗、低成本和灵活的解决方案,支持从200 kHz到56 MHz的可调通道带宽,以及从47 MHz到6 GHz的广泛频率范围。轻松支持两个或多个固定位置之间传输数据,如无线网络桥接、无线回程等

- 毫微微蜂窝/微微蜂窝/微微蜂窝基站:AD9361BBCZ正是为此而设计的,支持TDD和FDD模式,以及3G和4G等多种蜂窝标准,如LTE、WCDMA、TD-SCDMA。AD9361BBCZ还可以实现多芯片同步,适用于MIMO或相干系统。

- 通用无线电系统:得益于AD9361BBCZ良好的可编程性,可以通过软件配置实现不同的无线功能,如调制、解调、编码、解码等,作为通用无线电系统的核心组件,提供高度集成的RF前端和数字接口,以及丰富的控制和监测功能。还可以与FPGA或DSP等处理器配合使用,实现高速数据处理和信号处理。