微芯(Microchip) PL502-37OC器件介绍_规格参数_引脚图_工作原理

微芯(Microchip) 的 PL502-37OC 芯片是一种电压控制的频率合成芯片(VCXO),它可以根据输入的晶体频率(12 MHz 到 25 MHz)和控制电压(0 V 到 3.3 V)产生一个可调节的 LVCMOS 输出信号(0.75 MHz 到 800 MHz)。

PL502-37OC器件介绍

微芯(Microchip) 的 PL502-37OC 芯片是一种电压控制的频率合成芯片(VCXO),它可以根据输入的晶体频率(12 MHz 到 25 MHz)和控制电压(0 V 到 3.3 V)产生一个可调节的 LVCMOS 输出信号(0.75 MHz 到 800 MHz)。 PL502-37OC具有高频率稳定性(±200 ppm),低相位噪声(-135 dBc/Hz @ 10 kHz offset),低功耗(40 mA @ 3.3 V)和小尺寸(16 引脚 TSSOP 封装)的特点,适用于各种通信、网络和数据存储应用。该芯片还具有分频器和倍频器功能,可以实现更灵活的频率配置。

PL502-37OC规格参数

- 产品种类: VCXO振荡器

- 制造厂商 微芯 (Microchip)

- 锁相回路: 是

- 电线数量: 1

- 工作温度: 0摄氏度~70摄氏度

- 安装类别: 贴片

- 分频器: 是

- 倍频器: 是

- 输入比率 / 输出比率: 1:1

- 输入差分:否

- 输出差分: 是

- 封装: 16-TSSOP

- 输入值: 晶体

- 电源电压: 2.97伏 ~ 3.63伏

- 最大频率: 800MHz

- 系列: PL502-37/38/39

- 输出格式: LVCMOS

- 频率: 12 MHz to 25 MHz

- 频率稳定性: 200 PPM

- 负载电容: 9.5 pF

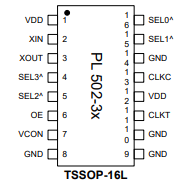

PL502-37OC引脚定义

引脚图

引脚定义:

| 名称 | TSSOP引脚号 | 类型 | 说明 |

| XIN | 2 | I | 晶体输入(参见第 4 页的晶体规格) |

| XOUT | 3 | I | 晶体输出(参见第 4 页的晶体规格) |

| OE | 6 | I | 输出使能引脚(参见第 1 页的 OE 逻辑状态表) |

| VCON | 7 | I | 电压控制输入 |

| GND | 8,9,10,14 | P | 接地连接 |

| CLKT | 11 | O | LVPECL 真输出 |

| CLKC | 13 | O | LVPECL 互补输出 |

| SEL0 | 16 | I | 倍增器选择引脚。这些引脚具有内部上拉功能,在未连接到接地时,SEL 默认为 "1"。 |

| SEL1 | 15 | I | |

| SEL2 | 5 | I | |

| SEL3 | 4 | I | |

| VDD | 1, 12 | P | +3.3V 电源。 |

| XIN | 2 | I | 晶体输入。 请参见第 4 页的晶体规格。 |

| XOUT | 3 | I | 晶体输出。 请参见晶体规格(第 4 页)。 |

| OE | 6 | I | 输出使能引脚(参见第 1 页的 OE 逻辑状态表)。 |

| VCON | 7 | I | 电压控制输入。 |

| GND | 8,9,10,14 | P | 接地。 |

| CLKT | 11 | O | LVDS True 输出(PL502-39) PL502-37 无连接 |

| CLKC | 13 | O | PL502-39 的 LVDS 互补输出 PL502-37 的 LVCMOS 输出 |

| SEL0 | 16 | I | 倍增器选择引脚。这些引脚具有内部上拉功能,当未连接至 GND 时,SELx 默认为 "1"。 |

| SEL1 | 15 | I | |

| SEL2 | 5 | I | |

| SEL3 | 4 | I | |

| VDD | 1, 12 | P | +3.3V 电源。 |

工作原理:

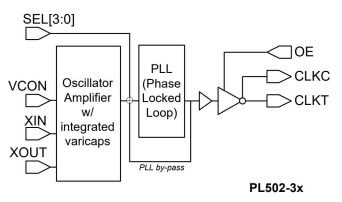

PL502-37OC原理图

PL502-37OC 根据晶体的频率和控制电压(0 V 到 3.3 V)产生一个可调节的 LVCMOS 输出信号(0.75 MHz 到 800 MHz)的原理如下:

PL502-37OC 使用一个频率在 12 MHz 到 25 MHz 之间的晶体作为输入信号的源头,将晶体的频率通过一个分频器(divider)降低到一个较低的值,将分频后的信号输入到一个锁相环(PLL)中,锁相环(PLL)将信号输入到倍频器(multiplier),以放大到一个较高的值,实现更高的输出频率,例如 800 MHz。最后,PL502-37OC将倍频后的信号通过一个缓冲器(buffer)输出到一个 LVCMOS 兼容的负载电路中。

其中:

- 分频器(divider)降低晶体的频率,可以提高 锁相环(PLL) 的锁相范围和速度

- 锁相环(PLL) 可以根据参考信号和反馈信号的相位差来调节输出频率

- LVCMOS 是一种低电压 CMOS 逻辑电平标准。