微芯(Microchip) MT9162AN1器件介绍_规格参数_引脚图_工作原理

MT9162AN1单轨编解码器内置滤波器/编解码器、传输抗混叠滤波器、基准电压和偏置源。

MT9162AN1器件介绍

微芯(Microchip)的MT9162AN1是一款5V单轨编解码器,MT9162 采用 Zarlink 的 ISO2-CMOS 技术制造,具有低功耗和高可靠性。

MT9162AN1集成了一个内置的滤波器/编解码器、一个发送抗混叠滤波器、一个参考电压和偏置源。支持 A-law 和 µ-law 要求。6dB的发送路径增益 ,模拟接口可驱动 20k 欧姆负载,具有SSI 数字接口。MT9162AN1采用20引脚SSOP封装,符合 ITU-T G.714 标准,属于电信接口芯片中的编解码器。

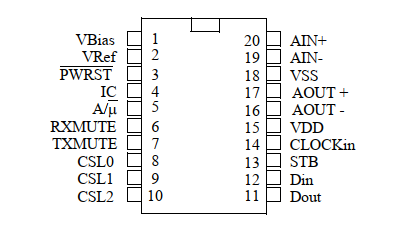

MT9162AN1引脚定义

| 引脚 | 引脚名 | 说明 |

|---|---|---|

| 1 | VBias | 偏置电压(输出)。 该引脚可提供 (VDD/2) 伏电压,用于为外部放大器提供偏置电压。将 |

| 0.1 mF 电容至 VSS。将 1 mF 电容连接至 Vref。 | ||

| 2 | VRef | 编解码器参考电压(输出)。 标称 [(VDD/2)-1.9] 伏。内部使用。将 0.1 |

| m F 电容连接至 VSS。将 1 mF 电容连接至 VBias。 | ||

| 3 | PWRST | 上电复位。 通过施密特触发器输入(低电平有效)复位设备内部状态。 |

| 4 | IC | 内部连接。 外部连接至 VSS,用于正常操作。 |

| 5 | A/m | A/m 法选择。 CMOS 电平兼容输入引脚,用于控制设备使用的压缩法则。 当引脚与 VDD 连接时选择 A-law,当引脚与 VSS 连接时选择 m-law。 |

| 6 | RXMute | 接收静音。1 时,发送 PCM 强制为负零码。0 时,正常工作。兼容 CMOS 电平。 |

| 7 | TXMute | 发送静音。1 时,发送 PCM 强制为负零码。0 时,正常运行。兼容 CMOS 级。 |

| 8 | CSL0 CSL1 CSL2 | 时钟速度选择。这些引脚用于设置 SSI 模式的速度,以及外部提供的 MCL 时钟与滤波器/编解码器所需的 512 kHz 时钟之间的转换率。 |

| 9 | 详情请参阅表 2。兼容 CMOS 电平。 | |

| 10 | ||

| 11 | Dout | 数据输出 三态数字输出,用于向第 1 层设备发送 8 位宽通道数据。在 STB 定义的时隙内,数据通过该引脚与 BCL 上升沿同时移出。 |

| 12 | Din | 数据输入 来自第 1 层设备的 8 位宽数据的数字输入。在 STB 定义的时隙内,BCL 的下降沿对数据进行采样。兼容 CMOS 电平。 |

| 13 | STB | 数据选通。 该输入决定了设备用于发送和接收数据的 8 位时隙。该高电平有效信号的重复频率为 8 kHz。兼容 CMOS 电平。 |

| 14 | CLOCKin | 时钟(输入)。设备内部功能使用该输入引脚提供的时钟。当位时钟频率为 512 kHz 或更高时,将其连接至该引脚。当位时钟为 128 kHz 或 256 kHz 时,将 4096 kHz 时钟连接至该引脚。兼容 CMOS 电平。 |

| 15 | VDD | 正电源。标称电压 5 伏。 |

| 16 | AOUT- | 反相模拟输出。(平衡)。 |

| 17 | AOUT+ | 非反相模拟输出。(平衡)。 |

| 18 | VSS | 接地。 标称 0 伏。 |

| 19 | Ain- | 反相模拟输入。 无需外部抗混叠。 |

| 20 | Ain+ | 非反相模拟输入。非反相输入。无需外部抗混叠。 |

工作原理

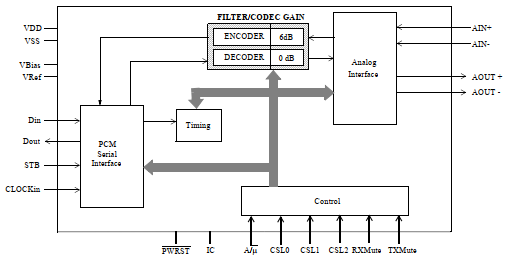

如上图所示,MT9162AN1内部由以下主要模块组成:

- Filter/Codec(滤波/编解码器):实现了模拟语音信号与数字PCM信号之间的转换,支持ITU-T G.711 A-律或μ-律压缩,同时提供模拟领域中的音频增益。它还包括滤波器以满足ITU-T G.714规格。

- Analog Interfaces(模拟接口):提供标准的模拟输入(发射机)和模拟输出(接收器)接口,支持不同压缩法则。

- PCM Serial Interface(PCM串行接口):与外部数字传输设备之间传输数据的串行接口,使用简单串行接口(SSI)模式。还支持静音码传输。

- SSI Mode(SSI模式):SSI操作分为同步和异步模式,取决于可用的比特时钟频率。芯片支持B通道操作,并需要4.096 MHz主时钟来派生内部时钟。

应用领域

MT9162AN1是一款通用编解码器可以用于电信领域,例如电话系统、语音信箱、语音导航、语音广告等。主要优势在于支持多频度(MFC)信号的生成和检测,以及多种语音编解码算法,如G.711、G.723.1、G.729A等。还具有高性能的A/D和D/A转换器,以及低功耗和低噪声的设计。