DDR Dram的刷新时间,芯片开发大神必须掌握的知识点

在众多消费电子芯片中,DDR的使用无处不在,电脑,手机等等。我们都知道,存储器分为易失和非易失两种,即所谓的掉电后,存储内容依然在,和掉电后消失的。

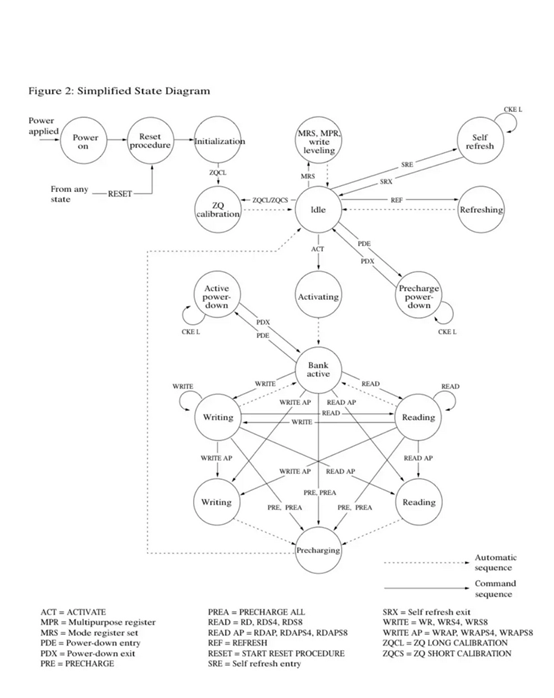

DDR初始化图

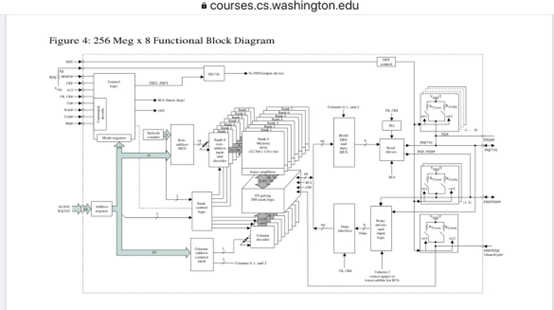

DDR内部结构图

非易失性的存储器有rom,eprom,e2rom,flash,efuse等,非易逝的又可以分为一次性可编程和多次可编程,这里不做过多的说明。

易失性存储器分为静态和动态的,静态就是RAM,读写接口简单,易于控制,读写速度快,一般用作缓存,像L1,L2 cache都是静态的,但是存储容量少,价格昂贵。

动态的就是SDRAM,DDR2,DDR3,DDR4,LPDDR都属于动态RAM,所谓动态就是,需要不断的进行刷新,数据才能保持,否则数据超过一定时间就会丢失,因为数据本质是电容存储的电量。

这里我们重点讲一下在芯片设计中,或者ddr控制器设计过程中,需要理解的一个概念,“刷新”。刷新就是循环充电,有一个重要的时间tref为7.8us,和64ms这两个时间。

这两个值都是JESD79-3DDR协议规定的,即,DDR3中一行的刷新时间最大不要超过7.8us,一个bank不要超过64ms,这样就从标准上限制了DDR中一个bank的行数,即64ms/7.8us,约等于8205,所以DDR3中一个bank的行数按照8192设计,置于数据位宽,可以是4bit,8bit,16bit,32bit,也就决定了DDR的存储容量。

这个是DDR中最重要的概念,也是DDR相关岗位面试中最常问的问题,有没有做过DDR相关工作,这一个问题就可以反映出来,所以大家一定要理解根本原因,也不知道大家明白没有,如果没有的话,可以加关注,注意后续文章,也可以阅读DDR协议。