数字信号想在芯片内部传输,竟然也要过这两大难关

在之前的文章中,我们介绍了,在综合过程中,综合工具(例如Design Compiler)需要知道单元模块的很多特征信息才能开始工作,例如输入信号的驱动能力,单元模块自己的负载大小,信号在不同驱动能力以及不同负载之下的速度以及功耗等等信息...

在之前的文章中,我们介绍了,在综合过程中,综合工具(例如Design Compiler)需要知道单元模块的很多特征信息才能开始工作,例如输入信号的驱动能力,单元模块自己的负载大小,信号在不同驱动能力以及不同负载之下的速度以及功耗等等信息。为了让综合工具很好的得到这些必须的信息,把这些数据放到一个库里面,就是工艺单元库。

EDA综合工具在综合过程中,根据用户所加的约束条件(时钟频率、面积等),开始将RTL映射到具体的工艺库里面,完成综合过程。以Synopsys公司的EDA综合工具Design

Compiler(DC)为例,DC在合成过程中,时钟频率的约束优先级最高,也就是说,首先必须满足时序的要求。那怎么就算满足时序要求了呢?

综合过程中的延时

通俗的讲,就是说信号从一个起点开始,经过逻辑门和导线传输,到达终点,如果整个耗时小于要求的时间,则认为满足时序要求,反之,则认为出现了时序违例,需要重修时序,这就是另外一个话题了,今天暂且不表。

信号在传输过程中的延时,主要分为两部分,经过逻辑cell的延时,我们称之为cell delay。在导线上面传输延时,我们称之为wire delay。所以可以简单的认为延时分为两部分,cell delay + wire delay。

需要说明的是,这个公式并不严谨。在实际的静态时序分析中(以setup分析为例),还必须考虑信号从寄存器的时钟端(CLK)到输出端(Q端)的时间,即C-Q时间,以及uncertainty,setup的时间,但是如果单独分析delay,可以简单的这么认为。

cell delay的计算方式

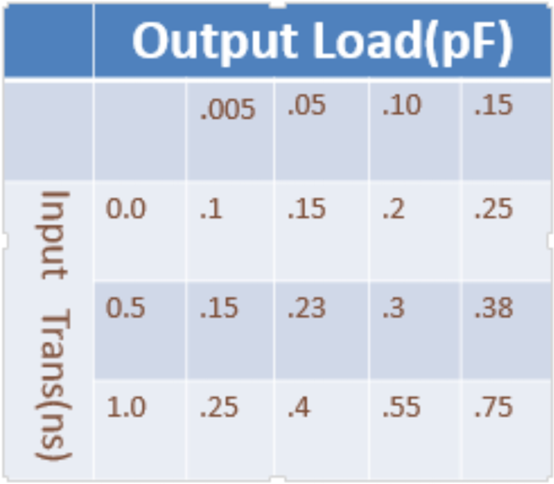

如果我们指定delay_model为table_lookup,则意味着我们在计算路径延时的时候,采用查找表的方式。具体的查表过程是(以计算cell

delay为例),以输入transition time和输出负载为横纵坐标,查表得到cell delay,如下图所示。

wire delay的计算方式

随着工艺水平的发展,线延时在整个信号delay中所占的比例,越来越高,所以对线延时不可以掉以轻心。

如果是在布局布线之后,那么wire delay的计算就不是很难。但是如果是在布局布线之前,我们该怎样估算wire delay呢?

Design Compiler在综合过程中,会首先从lib中获取单元尺寸的相关信息,然后,根据这些信息,估计目标电路的尺寸。获得这一尺寸之后,再使用线负载模型(wire load model)估计电路的wire delay。

所以很明显,估计的wire

delay是否准确,和采用的wire load model的准确性,呈现出正相关的强关系。因为wire load

model中的数据都来自于经验,所以必须有足够多的实践数据来进行支撑,也就意味着,这个model已经成功应用于很多设计实例中。当然,因为经验的局限性,对于一些之前没有实践支撑的部分,则通过估算得到。

小结

今天我们了解到芯片里面delay分为cell delay和wire delay,并且给出了两种delay的计算方式。那么EDA工具究竟是如何根据wire load model进行估算wire delay值的呢?欢迎继续关注后面的文章。