反击ASML,佳能发布NIL纳米压印5nm芯片光刻机,国产芯有何启示?

根据最新公开消息,佳能(Canon)最新发布光刻机是FPA-1200NZ2C,这款光刻机是应用纳米压印(Nanoprinted

lithography,NIL)技术的芯片生产设备。佳能的NIL技术可以实现最小线宽为14纳米,相当于目前可生产的绝大多数先进逻辑半导体的5nm节点。此外,随着掩模技术的进一步改进,NIL有望实现最小线宽为10纳米的电路图案,这相当于2nm节点。据了解,台积电和韩国三星这两家最大的半导体制造商都计划在2025年开始生产2纳米产品。

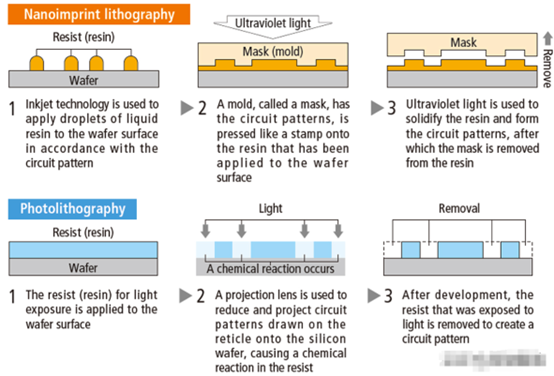

与传统的光刻设备不同,该设备通过将电路图案压印在涂覆在硅片上的光刻胶上来完成电路图案的传输,而新产品则通过将带有电路图案的掩模按压在硅片上的光刻胶上,类似于印章的方式来实现。由于其电路图案传输过程不涉及光学机构,因此掩模上的精细电路图案可以忠实地复制到硅片上。因此,可以在单个压印中形成复杂的二维或三维电路图案,从而降低了拥有成本(CoO)。

纳米压印技术是一种将电路图案转移至晶圆表面的技术,通过在晶圆表面压印具有电路图案的掩膜,实现电路图案的转移。佳能FPA-1200NZ2C光刻机通过将掩膜上的电路图案转移到晶圆上,能够制造出高精度的芯片。

图中展示了光刻过程的几个步骤,包括曝光、化学反应和去除。其中,曝光使用的是投影透镜来照射到硅片上的光刻胶上,从而形成图案。化学反应是通过在硅片上产生化学反应来实现的。最后,去除过程使用的是紫外线灯来清除未被固化的光刻胶,从而形成电路图案。

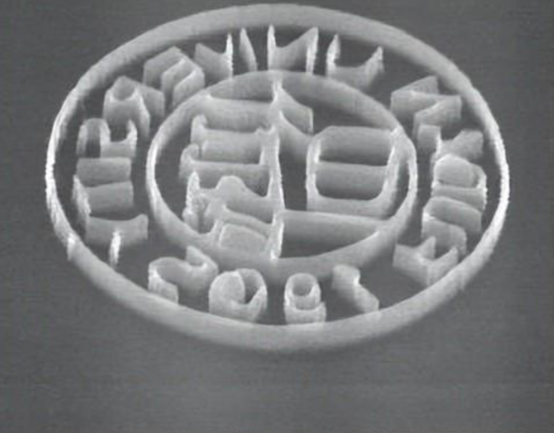

压印也不神秘,它其实是一门古老的图形转移技术,中国的活字印刷术就是最初的压印技术的原型。打一个通俗的比喻,压印就像是把一个刻有凹凸图案的章盖在橡皮泥上,然后在橡皮泥上留下了具有和章的图形相反的图案。只不过在纳米压印中,这个具有凹凸图案的章的图案特征尺寸在几个纳米到几百个纳米,这个章在纳米压印中被称为模板;而这个橡皮泥在压印过程中用特殊的纳米压印胶。在2012年,复旦大学也发表过类似的研究,给出了是用电子束光刻技术制备的目前复旦大学最小的“Logo”模板,它的直径在3微米,而比划中最小的尺寸是100纳米。

自从华裔科学家周郁教授于1995年首次提出纳米压印概念以来,这项技术已经在学术界和产业界引起了高度重视。据报道,佳能最新的纳米压印(NIL)套刻精度为2.4nm/3.2nm,研发中NIL已经可以处理高达5nm的电路线宽,每小时可曝光超过100片晶圆,每个晶圆的功耗仅为使用EUV光刻的十分之一左右。因此,纳米压印技术被誉为微纳加工领域中第三代最有前景的光刻技术之一。

纳米压印光刻得到了存储器制造商SK海力士和东芝的积极推动,而铠侠(前身为东芝存储器)甚至在技术不成熟且缺陷率高的阶段对佳能的设备进行了测试。

佳能的NIL技术可以绕过EUV光刻机需要的光源技术的限制,制造出更先进的芯片。对于佳能发布的NIL纳米压印光刻机实现5nm的技术,对国产芯片的有个大胆的猜测,我们是否已经拥有类似技术?你怎么看?