锗——未来10年当中固态器件的救星

近70年前,贝尔电话实验室的两位物理学家——约翰•巴丁和沃尔特•布拉顿——将两个很薄的金制触片压到一个锗片上,并将第三个触片置于该锗片的下方。通过这一装置的电流可以被用来放大信号。这就是历史上的第一个晶体管。这种放大器和开关可以说是20世纪最伟大的发明。在摩尔定律的支持下,晶体管为人类带来了在20世纪50年代不可能想象到的电脑。

近70年前,贝尔电话实验室的两位物理学家——约翰•巴丁和沃尔特•布拉顿——将两个很薄的金制触片压到一个锗片上,并将第三个触片置于该锗片的下方。通过这一装置的电流可以被用来放大信号。这就是历史上的第一个晶体管。这种放大器和开关可以说是20世纪最伟大的发明。在摩尔定律的支持下,晶体管为人类带来了在20世纪50年代不可能想象到的电脑。

尽管在晶体管的早期历史中,锗曾担当主角,但很快就被硅所取代。不过,现如今这种材料又回来了。世界上一些顶尖的芯片制造商正在考虑修改晶体管的核心——输送电荷的沟道。这种想法是用电流移动速度更快的材料代替硅。拥有此类沟道的晶体管能够帮助工程师继续制造出速度更快、能效更高的电子电路元件,也就意味着未来几年中可以设计出更好的电脑、智能手机和不计其数的其他设备。

长久以来,人们对于替代性沟道的研究均围绕着III-V族材料展开,如砷化镓,其构成原子就位于元素周期表中硅元素的左右两列。我本人也非常积极地参与了这方面的研究。事实上,我在8年前就为Spectrum撰写了一篇专题文章,报道了利用III-V族材料构建晶体管沟道的进展。

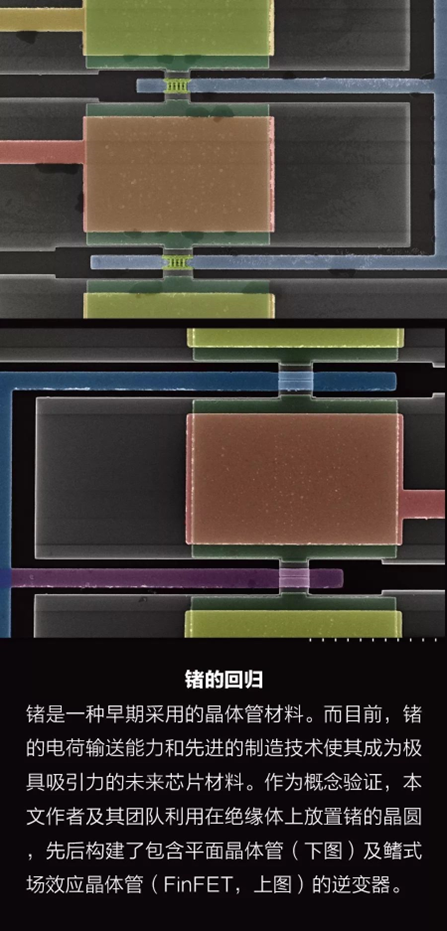

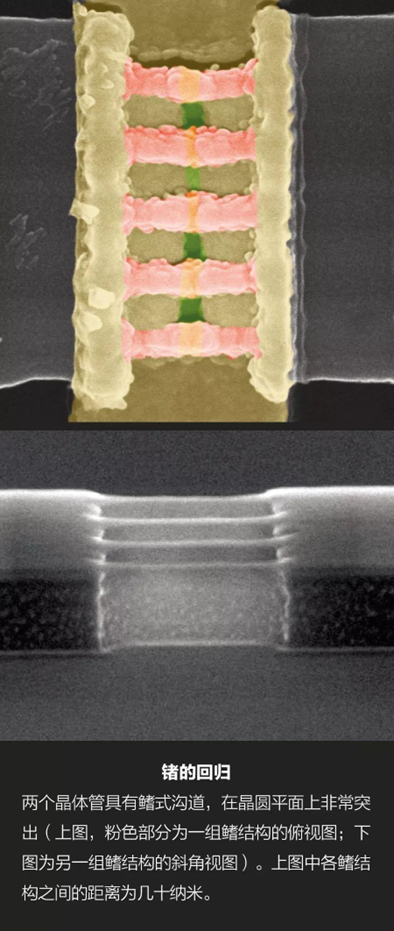

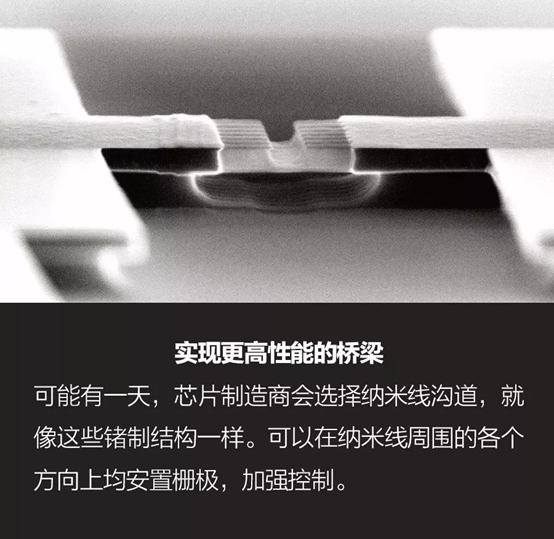

然而,最终我们发现,使用III-V族材料的方法还是有一些根本性的物理局限,而且太过昂贵,也很难与现有的硅技术相融合。因此,几年前,我所在的普渡大学(位于美国印第安纳州西拉法叶市)团队开始对另外一种器件进行实验——基于锗沟道的晶体管。在此之后,我们将锗植于普通的硅晶圆上,推出了首个互补金属氧化物半导体(CMOS)电路,也就是现今电脑内部的那种逻辑系统。我们还利用此材料制造了一系列不同的晶体管架构,包括纳米线器件。如果尖端晶体管设计——鳍式场效应晶体管(FinFET)无法继续实现微型化,这种纳米线器件可能成为下一代晶体管设计的首选。

最好的消息是,这些事实证明,锗的回归并没有想象的那么困难。据说,在沟道中同时使用硅和锗的晶体管已经出现在当前的一些芯片中,而且也已经在IBM及其合作伙伴们的2015年未来芯片制造技术展示中亮相。这可以说是产业趋势发展的第一步,未来沟道中的锗含量将越来越高。也许几年后我们就会发现,这种材料把晶体管带给了我们,如今又将晶体管引入了一个新的卓越性能时代。

锗是由德国化学家克雷门斯•温克勒在19世纪末期首次发现并分离的。为纪念温克勒所做的贡献,该元素以其家乡的名字命名,长期以来被认为是一种导电能力很差的金属物质。然而,这种看法却在二战期间发生了改变,人们发现锗具备一些半导体的特性,可以在导通或阻断电流的状态之间切换。战后的几年中,基于锗的固态器件层出不穷。而美国的锗产量从1946年的几百磅猛增到了1960年的45吨以上。但最后还是硅胜出,成为逻辑和存储芯片的首选材料。

硅能占据统治性地位是有合理理由的。一方面,硅的储量更高,且价格更为低廉,同时还有更大的带隙,带隙即晶体管传导电流必须克服的能量门限。带隙越大,电流越难在设备应处于关闭状态时发生泄漏,从而能减小功率损失。另外,硅还具备更好的导热性能,更容易散热,能够防止电路过热。

鉴于硅的种种优势,人们对锗重返沟道舞台自然也就会产生疑问。答案就是电子迁移性。室温条件下,电子在锗中的移动速度大约是其在硅中移动速度的3倍。而空穴(材料中出现电子空位而被当作正电荷对待)在锗中则可轻易地以4倍的速度移动。

锗中电子和空穴的高迁移性使得这种材料能够成为制造CMOS电路的优秀候选材料。CMOS使用两种不同的晶体管:沟道中包含过量自由移动空穴的p沟道FET(pFET),以及包含同样过量电子的n沟道FET(nFET)。电子和空穴的移动速度越快,最终的电路速度也越快。由于驱动这些载荷电子所需的电压低,因此也可以大大减少电路的能耗。

当然,锗并不是唯一具备高电子迁移性的材料。前面所提到过的III-V族化合物,如砷化铟和砷化镓等材料,也具有卓越的电子迁移性。事实上,砷化铟中电子的迁移性是硅的30倍。说到这儿,似乎一切都很好。但问题是砷化铟中的空穴没有这种卓越的特性,比不上硅中空穴的迁移性。该局限性会使pFET无法具备高性能,继而无法实现CMOS高速电路,因为设计不能接受nFET和pFET之间有太大的速度差异。

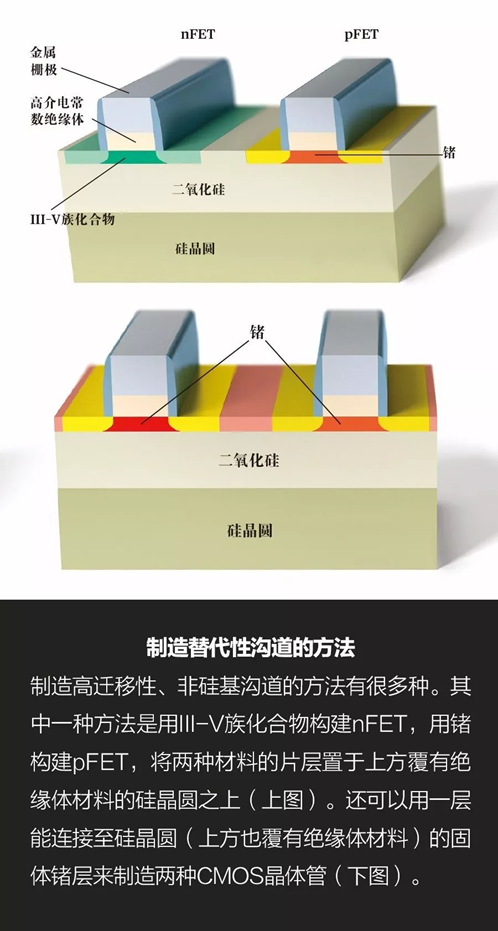

有一种可能的解决方案是使每种材料都得到充分利用。欧洲半导体研究组织欧洲微电子研究中心(Imec)和IBM苏黎世实验室等研究机构,已经展示出一些电路制造方式,制造出的电路同时包含基于III-V族材料的nFET沟道以及基于锗的pFET沟道。该技术可以实现高速电路,但也让制造流程变得更加复杂。

不论是基于上述原因还是其他原因,我们都更青睐于使用全锗制造方式。锗沟道能大大提高性能,而且制造方面的挑战也将更容易解决。

━━━━━

为了实现锗——或其他任何替代性沟道材料——的大规模量产,我们必须想办法将其置于当前用于制造芯片的餐盘大小的硅晶圆之上。幸运的是,有很多种方法可以在硅晶圆上构建锗层,之后再将其制成沟道。薄薄的一层即可以极大地减轻锗材料的两大关键性问题——比硅更高的成本和较差的导热性。

然而,取代晶体管沟道中的硅,并不仅仅是加入薄薄的一层高品质锗这么简单,还要保证沟道与晶体管其他部分之间的无缝协作。

如今无处不在的CMOS芯片中使用的是金属氧化物半导体场效应晶体管(MOSFET)。MOSFET有4个基本部分:源极和漏极,也就是电流的起点和终点;将其连接起来的沟道;以及栅极,相当于控制电流能否通过沟道的阀门。

在实际情况中,一个尖端的晶体管中还有其他一些组成部分。其中一个重要组成部分就是防止栅极和沟道短路的栅极绝缘体。半导体中的原子,如硅、锗以及包括砷化镓在内的III-V族化合物,均为三维排列结构。由于无法制造出完全平整的表面,因此沟道上的原子就会出现一些悬挂键。我们想得到的就是一个能够把尽可能多的悬挂键连接起来的绝缘层,这一过程叫做钝化处理。若处理得不好,就会出现“电崎岖”沟道,很多地方的电荷输送会受到暂时性的阻碍,进而降低移动性和设备速度。

幸亏大自然为硅提供了一个高质量的“原生”绝缘体,与其晶体结构非常匹配,这种绝缘体就是二氧化硅(SiO2)。虽然现如今的尖端晶体管用的是其他绝缘体,但仍包含了一层薄薄的该原生氧化物,用于硅沟道的钝化。由于硅和二氧化硅结构相近,因此一层经过良好处理的二氧化硅可以实现每10万悬挂键(大约相当于每平方厘米硅中所含的数量)中9.9999万悬挂键的连接。

砷化镓和其他III-V族材料没有原生氧化物,但锗有自己的原生氧化物,因此从理论上讲,存在一种可用于锗制晶体管沟道钝化的理想材料。但问题是二氧化锗(GeO2)比二氧化硅更弱,在芯片制造过程中很容易吸收用于清洗晶圆的水,甚至是被水溶解。更糟糕的是,二氧化锗的形成过程很难控制。尖端设备需要的是一层1至2纳米厚的二氧化锗,但要想制造出厚度低于20纳米的二氧化锗层都非常难。

研究人员已经对一些替代性方案展开了研究。斯坦福大学教授克里希纳•萨拉斯沃特(Krishna

Saraswat)及其同事们早在21世纪初就对使用锗作为替代性沟道材料的想法产生了兴趣,他们也首次发现了二氧化锆(ZrO2)这种用于高性能晶体管的“高介电常数”绝缘体。在该团队工作成果的基础上,比利时鲁汶Imec的一个小组开展了相关研究,想了解如何处理超薄硅层,以改进锗和这种高介电常数材料之间的交界面。

在2011年,锗的钝化处理有了一个大的飞跃。东京大学教授高木真一(ShinichiTakagi)带领的团队找到了一种控制锗绝缘体生长的方法。首先,研究人员会在锗沟道上形成一层纳米级厚度的高介电常数绝缘体氧化铝,然后将器件整体放入一个充满氧气的腔室中。一小部分氧气会经过氧化铝层到达下面的锗,并与锗结合成为一层薄薄的氧化物(锗与氧的结合物,但严格意义上说并不是二氧化锗)。除了有助于控制生长过程之外,氧化铝还相当于这层较弱、较不稳定的物质的保护罩。

━━━━━

几年前,受该成果的启发,面对用III-V族沟道制造pFET过程中所面临的诸多困难,我和我在普渡大学的团队开始寻找制造锗沟道晶体管的方法。一开始我们用的是法国晶圆制造商Soitec开发的锗绝缘晶圆。这类晶圆是标准的硅晶圆,覆有一层电绝缘体,绝缘体上方是一层100纳米厚的锗。

利用这些晶圆,我们就可以将晶体管中的所有标准硅部件都替换成锗,包括源极、沟道和漏极区域。这并不是说芯片制造商就一定会使用这种方法制造晶体管,但这种方法比较方便我们对锗制设备的基本特性展开研究。

我们一开始遇到的问题之一就是如何解决晶体管源极和漏极区域之间的电阻,并找到将其与外界相连的金属电极。这种电阻来自于一种天然的电势垒——肖特基势垒,其在金属和半导体相接触时产生。人们一直在不停地改进晶体管,使该势垒尽可能薄,便于电荷隧穿。但要想在锗器件上实现同样的效果则需要一些巧妙的设计。由于在电结构方面的细微差别,空穴可以轻易从一种金属移动到锗,但电子却无法实现。也就是说,依靠电子运动的nFET会有非常大的电阻,产生废热,在高速电路中只能引导很少一部所需的电流。

将势垒做薄的标准做法是在源极和漏极区域加入更多的掺杂剂原子。这里所包含的物理原理非常复杂,但我们可以这么想:掺杂剂原子越多,自由电荷也就越多。大量自由电荷可以增强金属电极、半导体源极与漏极区域之间的电相互作用。更强的耦合有助于电荷在势垒中隧穿。

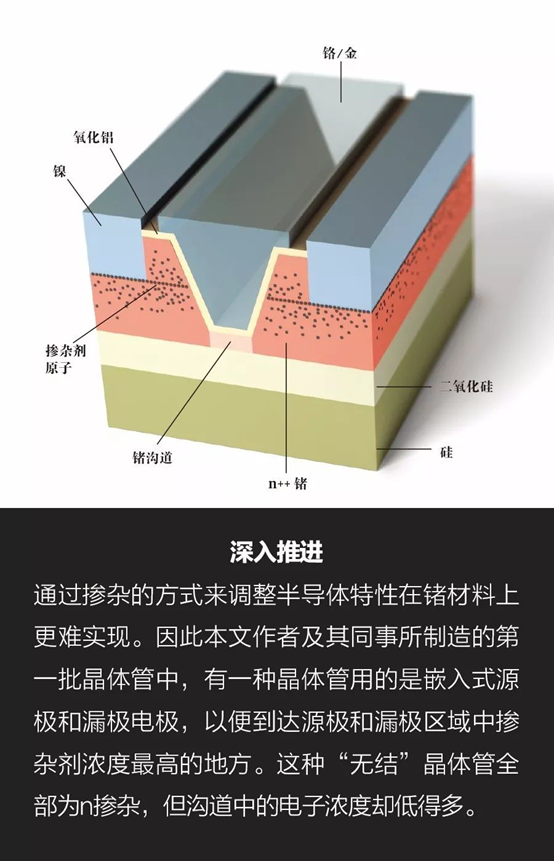

遗憾的是,这种技术在锗中的表现没有在硅中那么好;这种材料无法承受将肖特基势垒做薄所需的、贡献电子的高浓度掺杂剂。我们能做的就是深入到掺杂剂浓度最高的地方去。

我们可以借鉴尖端半导体中的掺杂方法实现上述目标,通过超高电场将离子推入材料中。一些掺杂剂原子很快就会停止移动;但还有一些则可以深入。最终,我们会得到一条正态分布曲线:在某一深度的掺杂剂原子浓度最高,随着深度变浅或变深而逐渐下降。若我们把源极和漏极电极嵌入半导体材料中,就可以使其接触最高浓度的掺杂剂原子。此方法大大缓解了接触电阻问题。

不论芯片制造商最终是否会选择使用该方法将锗中的肖特基势垒做薄,这都是对锗材料性能的有益展示。研究初期,最优的锗制nFET可以在每微米宽度内产生100安培的电流。2014年,我们在于夏威夷举行的超大规模集成电路(VLSI)技术与电路研讨会上发布了一种锗制nFET,其创纪录地产生了10倍于上述数字的漏极电流,几乎和硅持平——初期就能达到这样的水平还是很可观的。6个月之后,我们发布了第一批同时包含锗基nFET和pFET的电路,这也是制造现代逻辑芯片的前提条件。

自那以后,我们用锗设计出了更加先进的晶体管,如FinFET——当前最尖端的晶体管技术。我们还制造出了锗基纳米线晶体管,在未来的几年内可以很好地取代FinFET。

我们可能还需要用这些先进的晶体管设计来推动锗在大规模生产中的应用,因为它们可以更好地控制晶体管沟道。由于锗的带隙较小,因此锗沟道晶体管所需的能量仅为硅沟道晶体管切至导电状态时所需能量的1/4。这就为低功率操作提供了可能性,但也会使电流在开关处于关闭状态时更容易发生泄漏。沟道控制性更好的器件可以使芯片制造商在不影响开关性能的情况下利用较小的带隙。

良好的开端并不意味着目标的完成,我们还有更多的工作要做。一方面,我们需要做更多的晶圆实验,制造出具备高质量锗沟道的晶体管。另一方面,我们也需要继续改进器件设计,进一步提高速度。

当然,锗并不是未来唯一的一种晶体管沟道选择。研究人员会继续对III-V族材料展开探索,可以配合锗一起使用,也可以单独使用。未来还会有很多其他可能的晶体管改进方式,包括碳纳米管晶体管、垂直定向开关、3D电路、锗锡混合沟道以及量子隧穿晶体管。

在未来的几年中,我们可能最终会选择其中的几种技术。但在沟道中加入锗——哪怕开始时是与硅混合使用——确实是一种解决方案,让芯片制造商在短期内能够持续改进晶体管技术。锗作为固态年代最早使用的材料,可能会成为未来10年当中一种强有力的灵丹妙药。