美国微芯_ATMEGA16A-AU介绍_规格参数_优缺点_引脚_工作原理_封装_AVR增强型RISC架构

ATMEGA16A-AU是美国微芯公司的一款基于Atmel AVR增强型RISC架构的16位低功耗高性能CMOS微控制器。该器件具有16KB自编程闪存程序存储器、1024B SRAM、512byte EEPROM、8通道10bit A/D转换器和用于片上调试的JTAG接口

ATMEGA16A-AU器件介绍

ATMEGA16A-AU是美国微芯公司的一款基于Atmel AVR增强型RISC架构的16位低功耗高性能CMOS微控制器。该器件具有16KB自编程闪存程序存储器、1024B SRAM、512byte EEPROM、8通道10bit A/D转换器和用于片上调试的JTAG接口。它在2.7至5.5V的工作电压下,16MHz时可实现16 MIPS的吞吐量。

通过在一个时钟周期内执行功能强大的指令,该设备可实现接近1 MIPS/MHz的吞吐量,从而使用户能够优化功耗与处理速度。Atmel AVR内核将丰富的指令集与32个通用工作寄存器结合在一起。所有的32个寄存器都直接连接到算术逻辑单元(ALU),从而允许在一个时钟周期内执行的一条指令中访问两个独立的。

ATMEGA16A-AU采用44引脚QFP封装,可广泛应用于各种电子设备和嵌入式系统中。作为一款低功耗高性能的微控制器,它在许多领域都有很好的应用前景,如智能家居、工业控制、医疗设备、汽车电子等。同时,其丰富的资源和强大的性能也为开发者提供了更多的可能性。

规格参数

- 电源电压:2.7V至5.5V

- 频率:16 MHz

- RAM大小:1 KB

- 位数:8

- FLASH内存容量:16 KB

- 输入/输出数:32

- 工作温度(Max):85 ℃

- 工作温度(Min):-40 ℃

- 安装方式:Surface Mount

- 引脚数:44

- 封装:TQFP-44

ATMEGA16A-AU器件的优缺点

优点:

- 基于Atmel AVR增强型RISC架构,具有丰富的指令集和高速的处理能力。

- 件具有多种省电模式,可以有效地降低功耗,延长设备的使用时间。

- 大容量存储,满足各种存储需求。丰富的外设接口,方便与外部设备通信。

- 支持片上调试,简化了开发和调试过程。

缺点:

- 制造成本较高。

- 功耗管理复杂。

- 对于某些应用,可能需要额外的外部元件或电路来支持其功能。

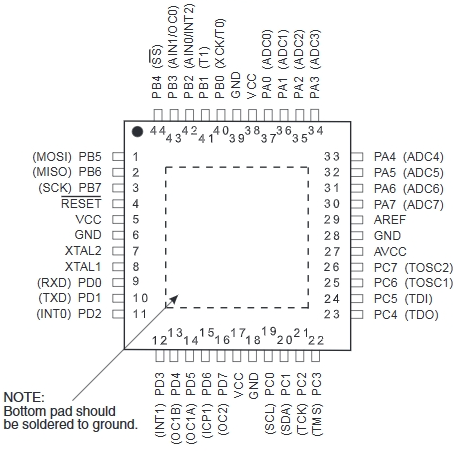

引脚图及引脚介绍

ATMEGA16A-AU器件的44个引脚分别是:

- PA0-PA7、PB0-PB7、PC0-PC7、PD0-PD7:数字I/O引脚,用于数字信号的输入和输出。

- RESET:复位引脚,用于触发器件的复位操作。

- 3个VCC:电源引脚,通常用于接入正电源电压。

- 4个GND:接地引脚,用于将器件连接到地线。

- AVCC:模拟电源引脚,为模拟电路提供电源。

- XTAL1、XTAL2:这两个是用于接入外部晶体的引脚。

- AREF:模拟参考电压引脚,用于为模拟电路提供参考电压。

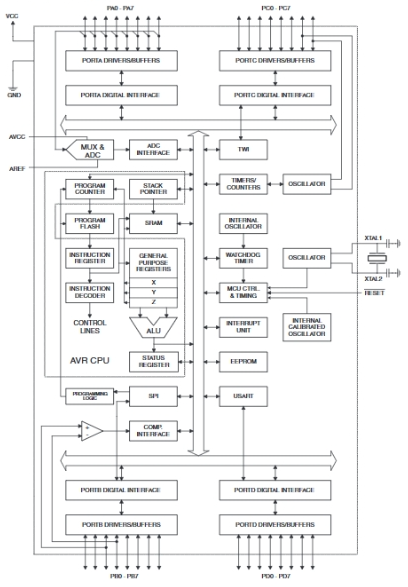

原理图及工作原理介绍

ATMEGA16A-AU器件是一款基于AVR增强型RISC架构的16位低功耗高性能CMOS微控制器,其工作原理涉及指令执行、数据存储与读取、外设交互、中断处理等多个方面,可以概括为以下几个步骤:

- 上电初始化:当器件上电时,程序计数器(PC)自动指向预设的启动地址(通常为Flash存储器中的第一条指令)。此时,ATMEGA16A-AU开始执行程序。

- 指令执行:微控制器从Flash存储器中读取指令,然后将其解码并执行。每条指令可能涉及算术逻辑单元(ALU)操作、数据传送、跳转或分支等操作。

- 数据存储与读取:ATMEGA16A-AU在执行指令过程中,可能需要在SRAM或EEPROM中存储或读取数据。这些操作通过内存映射的方式实现,即将内存地址映射到物理存储器中。

- 外设交互:ATMEGA16A-AU集成了多种外设,如A/D转换器、JTAG接口等。在执行程序过程中,可以通过读写特定的寄存器来控制和配置这些外设。

- 中断处理:在程序执行过程中,可能产生各种中断事件,如外部中断、定时器中断等。当中断产生时,ATMEGA16A-AU会暂停当前程序的执行,转而执行相应的中断服务程序。

- 时钟系统:ATMEGA16A-AU内部有一个精密的振荡器,用于产生系统时钟。用户可以根据需要配置不同的时钟源和分频器,以实现对器件工作频率的控制。

- 电源管理:ATMEGA16A-AU支持多种低功耗模式,如空闲模式、掉电模式等。在这些模式下,器件可以降低工作频率或关闭部分功能,以降低功耗。

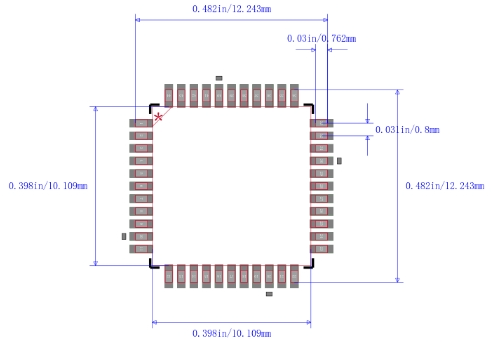

封装图

ATMEGA16A-AU器件的封装为TQFP-44。封装图如下所示:

什么是AVR增强型RISC架构,与其他架构有何不同?

AVR增强型RISC架构(Advanced Virtual RISC)是一种由Atmel公司开发的精简指令集计算(RISC)架构。RISC是一种计算机处理器架构,其设计理念是采用较简单的指令集和较高的处理速度。AVR架构在RISC的基础上进行了增强和优化,以提供更高的性能和更低的功耗。

AVR增强型RISC架构以其高效、低功耗、高性价比和灵活的特点,在嵌入式系统和电子设备领域得到了广泛应用。然而,与更高级的处理器架构(如ARM、x86等)相比,AVR架构在处理速度和功能上可能存在一定的局限性。

与其他架构相比,AVR增强型RISC架构有以下特点:

- 高效的流水线设计:AVR架构采用了高效的流水线设计,使得指令执行更加并行化,从而提高了处理器的性能。

- 丰富的指令集:AVR架构提供了丰富的指令集,包括算术、逻辑、数据传送、程序控制等指令,以支持各种应用需求。

- 低功耗设计:AVR架构采用了低功耗设计技术,可以在保持高性能的同时降低功耗,适用于电池供电和节能应用。

- 高性价比:AVR架构在性能和成本之间取得了良好的平衡,为嵌入式系统和电子设备提供了高性价比的解决方案。

- 灵活的存储器结构:AVR架构支持多种存储器结构,包括片上Flash、SRAM、EEPROM等,可以根据应用需求灵活配置。