STM32G030K6T6_如何管理STM32G030K6T6的时钟系统以优化性能

STM32G030K6T6是一款由意法半导体(STMicroelectronics)生产的微控制器。该微控制器基于高性能ARM Cortex®-M0 32位RISC内核,运行频率高达64MHz

STM32G030K6T6器件介绍

STM32G030K6T6是一款由意法半导体(STMicroelectronics)生产的微控制器。该微控制器基于高性能ARM Cortex®-M0 32位RISC内核,运行频率高达64MHz。它具有高速内嵌内存,包括高达32KB的闪存和高达8KB的SRAM。此外,STM32G030K6T6还集成了丰富的外设和输入输出范围,如标准通信接口(高达两个I2C,高达两个SPI和高达六个USART)、一个12位模数转换器以及7个通用定时器等。

STM32G030K6T6器件特点

- 核心:ARM Cortex-M0+ CPU,频率高达64 MHz。

- 存储:高达64kbytes的闪存保护,8kbytes SRAM,带HW奇偶校验。

- 电源管理:电压范围2.0 V ~ 3.6 V,上电/下电复位(POR/PDR),低功耗模式:睡觉、停止、待机。

- 时钟管理:4至48 MHz晶体振荡器,32千赫晶体振荡器校准,内部16 MHz RC与锁相环选项,内部32 kHz RC振荡器(±5%)。

- 外设接口:最多44个快速I/O,所有可映射到外部中断向量,多个5v容错I/O。5通道DMA控制器与灵活的映射,12位,0.4µs ADC(最多16个ext. channel),最高16位硬件过采样,转换范围0 ~ 3.6V。8个定时器:16位高级电机控制,4个16位通用,2个看门狗,SysTick定时器。日历RTC与报警和周期唤醒从停止/待机。

- 温度范围:工作温度范围-40°C至85°C。

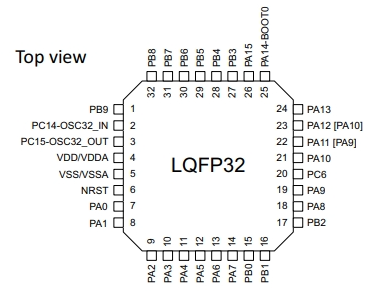

引脚图及引脚介绍

STM32G030K6T6器件的32个引脚如下所示:

- PA0-PA15,PB0-PB9,PC6,PC14,PC15:这些都是GPIO引脚,用于输入或输出数字信号。

- VSS:地引脚,用于连接设备的地线。

- VDD:电源引脚,用于提供设备的电源电压。

- NRST:复位引脚,用于触发微控制器的复位操作。

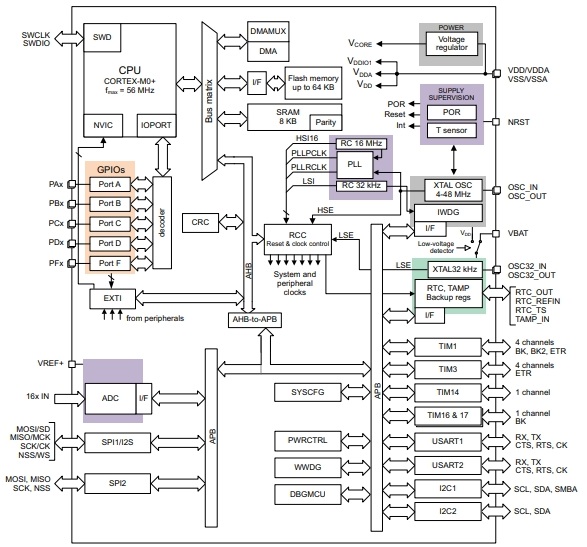

原理图及工作原理介绍

STM32G030K6T6的工作原理是通过内核执行程序代码,管理时钟系统,利用外设接口与外部设备通信,利用存储保护单元确保系统安全,以及利用低功耗模式降低功耗。

- 内核工作原理:ARM Cortex-M0+内核是该微控制器的核心,负责执行指令和控制硬件操作。它通过读取并执行存储在闪存中的程序代码来工作,这些代码通过一系列的运算和逻辑处理实现特定的功能。

- 时钟系统:STM32G030K6T6的时钟系统是其工作的节拍器,它由一个振荡器提供原始时钟信号,然后通过PLL(Phase Locked Loop)倍频和分频,得到系统所需的各种时钟频率。这些时钟信号控制着内核、外设和系统其他部分的工作。

- 外设接口工作原理:STM32G030K6T6具有丰富的外设接口,如I2C、SPI、UART等。这些外设接口通过内核的GPIO(General Purpose Input/Output)引脚与外部设备或传感器连接。当外设接口接收到相应的信号时,它会触发中断给内核,内核执行相应的中断服务例程(ISR)来处理这些信号,实现与外部设备的通信和控制。

- 存储保护单元(MPU):STM32G030K6T6集成了存储保护单元(Memory Protection Unit),它可以对程序存储器和数据存储器进行分区和保护,确保各个任务或中断服务例程之间的数据和代码不会相互干扰,提高了系统的安全性和稳定性。

- 低功耗模式:STM32G030K6T6具有多种低功耗模式,如睡眠模式、停止模式、待机模式等。这些低功耗模式可以在不需要或减少系统资源的情况下降低功耗,延长系统的工作时间。

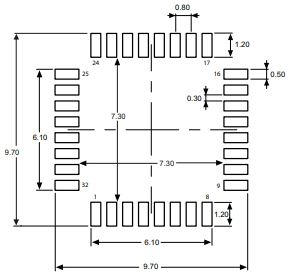

封装图

STM32G030K6T6器件的封装类型是LQFP-32。封装图如下所示:

如何管理STM32G030K6T6的时钟系统以优化性能?

管理STM32G030K6T6的时钟系统以优化性能主要涉及以下几个步骤:

- 了解时钟源:首先,需要了解STM32G030K6T6的时钟源。该微控制器可以从外部晶振、内部RC振荡器或PLL获取时钟。了解这些时钟源的特性和优缺点是关键。

- 选择合适的时钟源:根据应用需求选择合适的时钟源。例如,如果需要高精度的时钟,外部晶振可能是更好的选择。如果需要稳定的低功耗时钟,则内部RC振荡器可能更合适。

- 配置PLL:如果使用PLL,需要正确配置PLL以获得所需的时钟频率。这可能涉及选择适当的倍频器和分频器值。

- 关闭不必要的时钟:在某些情况下,关闭不需要的时钟源可以降低功耗。例如,如果某些外设在特定模式下不使用,可以关闭其时钟。

- 使用低功耗模式:根据应用需求,合理利用STM32G030K6T6的低功耗模式(如睡眠模式、停止模式、待机模式等)可以在不影响性能的情况下降低功耗。

- 考虑实时时钟(RTC)需求:如果应用需要实时时钟,确保RTC的时钟源配置正确,并考虑是否可以通过RTC的时钟源为其他外设提供时钟。

- 代码优化:编写高效的代码可以进一步优化性能。例如,避免不必要的循环和延时,使用中断而非轮询来处理事件等。

- 硬件和软件协同设计:有时,硬件和软件之间的协同设计对于性能优化至关重要。例如,某些外设的配置可能需要特定的软件模式或初始化序列。

- 测试和验证:最后,通过实际测试和验证来确保所做的更改确实提高了性能。这可能涉及比较不同配置的性能、测量功耗等。