AD7190BRUZ-REEL的低噪声可编程增益级如何实现?

AD7190BRUZ-REEL是一款超低噪声、24位Σ-Δ模数转换器(ADC),具有片上低噪声可编程增益级。它可以配置为两路差分输入或四路伪差分输入

AD7190BRUZ-REEL器件介绍

AD7190BRUZ-REEL是一款由ADI公司推出的超低噪声、24位Σ-Δ模数转换器(ADC),具有片上低噪声可编程增益级。它可以配置为两路差分输入或四路伪差分输入。片内通道序列器可以使能多个通道,AD7190按顺序在各使能通道上执行转换,简化了与器件的通信。其特性包括高精度测量、低噪声以及完整模拟前端等特点,适用于电子秤、应变计传感器、压力测量、温度测量、色谱、PLC/DCS模拟输入模块、数据采集以及医疗与科学仪器等多种应用。

AD7190BRUZ-REEL器件特点

- 超低噪声:AD7190BRUZ-REEL具有非常低的噪声特性,能够精确地测量微弱信号,使得它在需要高精度测量的应用中表现出色。

- 内置低噪声可编程增益级:器件内置了低噪声的可编程增益级,允许用户根据信号大小调整增益,从而可以直接连接小幅度信号到ADC,简化了电路设计。

- 多通道能力:AD7190BRUZ-REEL可以配置为两路差分输入或四路伪差分输入,通过片内通道序列器,可以按顺序在各使能通道上执行转换,提高了数据处理的灵活性和效率。

- 数字滤波器选项:器件提供了两种数字滤波器选项,可以根据具体的应用需求选择最合适的滤波器,以达到最佳的噪声性能、分辨率和建立时间。

- 高采样率和数据速率:AD7190BRUZ-REEL具有高达4.8kHz的采样率,并且输出数据速率可以在较宽的范围内变化,从而满足了不同应用对数据速率的需求。

- 同步功能:在多器件同步应用中,AD7190BRUZ-REEL可以实现同步操作,确保多个器件的数据寄存器同时更新,这对于需要高精度多通道同步采样的应用至关重要。

- 低功耗:AD7190BRUZ-REEL在提供高性能的同时,也注重功耗控制,采用5V模拟电源和2.7V至5.25V数字电源供电,功耗仅为6mA,使得它适合在功耗受限的应用中使用。

- 灵活的电源和接口选项:器件支持多种电源和接口配置,使其能够方便地集成到各种系统中。

- 出色的线性度和稳定性:AD7190BRUZ-REEL具有优异的增益误差和积分非线性度,保证了测量的准确性和稳定性。

引脚介绍

以下是AD7190BRUZ-REEL器件的24个引脚的详细介绍:

- MCLK1:外部时钟输入1,用于提供ADC的时钟信号。

- MCLK2:外部时钟输入2,用于提供ADC的时钟信号。

- SCLK:串行时钟输入,用于同步ADC的串行数据传输。

- CS:片选信号输入,用于选择ADC进行数据传输。

- P0-P3:编程输入引脚,用于设置ADC的内部寄存器。

- NC:无连接引脚,该引脚不与内部电路连接。

- AINCOM:模拟输入公共端,用于连接输入信号的公共端。

- AIN1-AIN4:模拟输入端,用于接收输入信号。

- REFIN1(+):参考电压正输入端,用于连接外部参考电压的正极。

- REFIN1(-):参考电压负输入端,用于连接外部参考电压的负极。

- BPDSW:温度传感器开关控制引脚,用于控制片内温度传感器的工作状态。

- AGND:模拟地引脚,用于连接ADC的模拟地。

- DGND:数字地引脚,用于连接ADC的数字地。

- AVDD:模拟电源输入引脚,用于为ADC的模拟部分供电。

- DVDD:数字电源输入引脚,用于为ADC的数字部分供电。

- SYNC:同步信号输入,用于同步ADC的内部时钟和外部时钟。

- DOUT/RDY:数据输出/就绪信号输出,用于输出ADC转换后的数字数据,或者表示ADC是否准备好接收新数据。

- DIN:数据输入引脚,用于输入ADC的内部寄存器数据。

原理图及工作原理

- 输入信号调理:AD7190BRUZ-REEL的模拟输入端(AIN1-AIN4)接收输入信号。这些信号可以通过内部的可编程增益放大器(PGA)进行放大。PGA的增益可以通过配置寄存器进行设置。此外,输入信号还可以通过内部的差分放大器进行差分放大。

- 模数转换:经过信号调理后的输入信号被送入Σ-Δ调制器进行模数转换。Σ-Δ调制器采用积分器和比较器实现高精度模数转换。在转换过程中,输入信号与一个高频参考信号进行比较,产生一个误差信号。该误差信号经过积分器积分后,再与参考信号进行比较,如此反复,实现高精度模数转换。

- 数据处理:模数转换后的数据经过内部数字滤波器进行滤波处理,以降低噪声和改善信号质量。数字滤波器的类型和参数可以通过配置寄存器进行设置。

- 数据输出:处理后的数据通过串行接口输出。数据输出引脚(DOUT/RDY)输出转换后的数字数据。同时,该引脚还可以表示ADC是否准备好接收新数据。

- 控制与同步:片选信号输入(CS)、串行时钟输入(SCLK)和数据输入引脚(DIN)负责与外部设备进行数据传输和同步。片选信号用于选择ADC进行数据传输,串行时钟用于同步数据传输,数据输入用于输入ADC的内部寄存器数据。

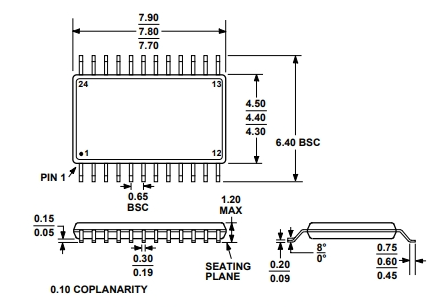

封装图

AD7190BRUZ-REEL器件的封装为TSSOP-24。封装图如下所示:

AD7190BRUZ-REEL的低噪声可编程增益级如何实现?

AD7190BRUZ-REEL的低噪声可编程增益级是通过集成的模拟前端实现的。该模拟前端包含一个可编程增益放大器(PGA),可以对输入信号进行放大,同时保持低噪声性能。PGA通过内部的数字控制逻辑实现可编程增益设置,用户可以通过配置寄存器来选择不同的增益值。

可编程增益级的实现主要依靠PGA内部的运算放大器和反馈电阻网络。运算放大器用于放大输入信号,反馈电阻网络用于设置运算放大器的闭环增益,从而实现可编程增益。在AD7190BRUZ-REEL中,PGA的增益设置范围和具体实现细节可能会有所不同,具体信息需要参考器件的数据手册。

通过这种方式,AD7190BRUZ-REEL可以实现低噪声可编程增益级,使得小幅度的信号可以直接连接到ADC,提高了系统的噪声性能和信号处理能力。