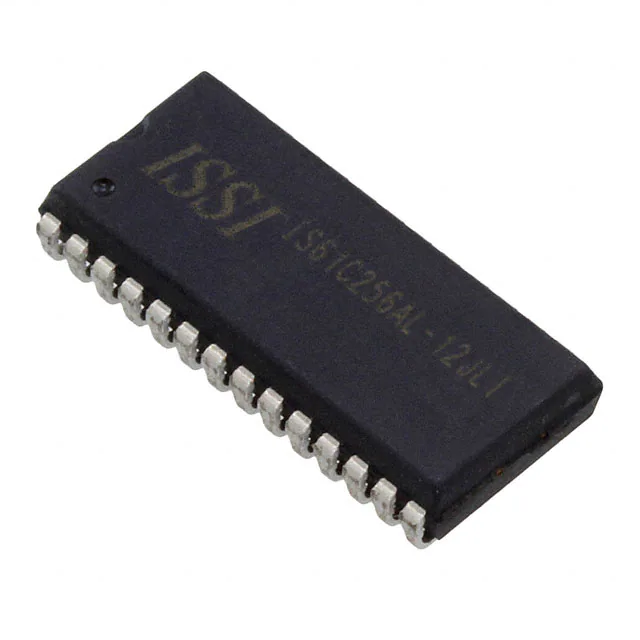

DESCRIPTION

The ISSI IS62WV25616ALL/IS62WV25616BLL are highspeed, low power, 4M bit SRAMs organized as 256K words by 16 bits. It is fabricated using ISSI's high-performance CMOS technology. This highly reliable process coupled with innovative circuit design techniques, yields highperformance and low power consumption devices. When CS1 is HIGH (deselected) or when CS1 is LOW and both LB and UB are HIGH, the device assumes a standby mode at which the power dissipation can be reduced down with CMOS input levels. Easy memory expansion is provided by using Chip Enable and Output Enable inputs. The active LOW Write Enable (WE) controls both writing and reading of the memory. A data byte allows Upper Byte (UB) and Lower Byte (LB) access. The IS62WV25616ALL/IS62WV25616BLL are packaged in the JEDEC standard 44-Pin TSOP (TYPE II) and 48-pin mini BGA (6mmx8mm).

FEATURES

• High-speed access time: 55ns, 70ns

• CMOS low power operation 36 mW (typical) operating 9 µW (typical) CMOS standby

• TTL compatible interface levels

• Single power supply

1.65V--2.2V VDD (IS62WV25616ALL)

2.5V--3.6V VDD (IS62WV25616BLL)

• Fully static operation: no clock or refresh required

• Three state outputs

• Data control for upper and lower bytes

• Industrial temperature available

• Lead-free available

(Picture: Pinout)