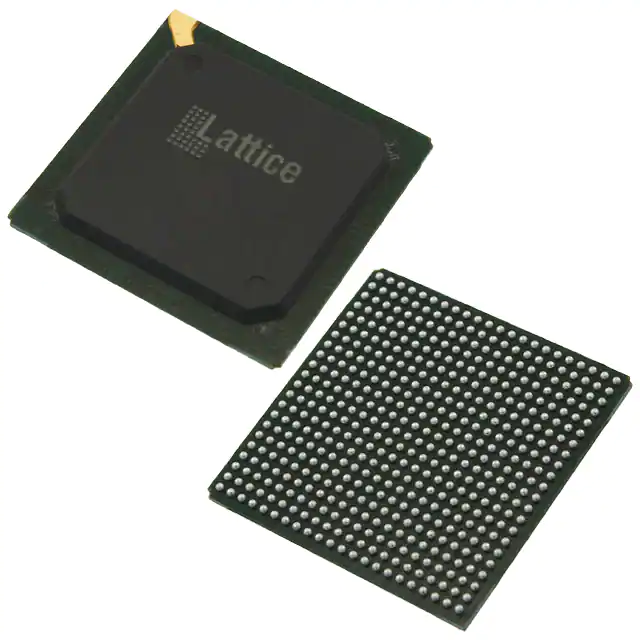

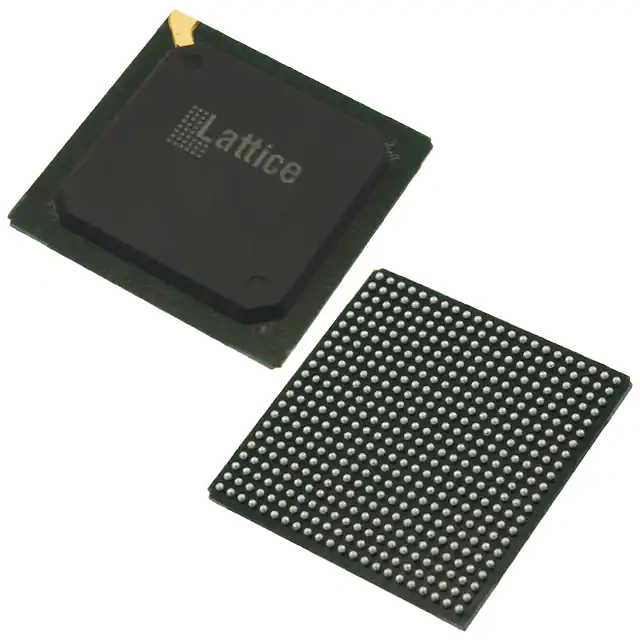

ORT42G5和ORT82G5-2FN680I为板上或背板上的设备间通信提供了无时钟高速接口。ORT42G5和ORT82G5-2FN680I的内置时钟恢复允许更高的系统性能,更容易在多板系统中设计时钟域,并且背板上的信号更少。网络设计者将受益于作为网络终端设备的背板收发器。该设备支持用于10G以太网和光纤通道的嵌入式8b/10b编码/解码和链路状态机。

ORT82G5-2FN680I与姊妹设备ORSO82G5的引脚输出兼容,ORSO82G5通过SONET加扰和小区处理实现了8个SERDES信道。ORT42G5与ORSO42G5引脚兼容,后者通过SONET加扰和信元处理实现四通道SERDES。

特色

•高性能可编程逻辑:

–0.16µm 7级金属技术。

–内部性能>250 MHz。

–超过400K可用系统门。

–符合多个I/O接口标准。

–1.5V操作(功率比1.8V操作低30%)可提高性能。

•传统I/O选择:

–LVTTL(3.3V)和LVCMOS(2.5V和1.8V)I/O。

–每引脚可选I/O箝位二极管提供3.3V PCI合规性。

–单独可编程驱动能力:24 mA汇点/12 mA源、12 mA汇点/6 mA源或6 mA

汇/3 mA源。

–支持两种转换速率(快速和转换受限)。

–快速捕获输入锁存器和输入触发器(FF)/锁存器,减少输入设置时间和零保持时间。

–快速开式排水驱动能力。

–能够注册三态启用信号。

–芯片外时钟驱动能力。

–输出路径中的双输入函数发生器

•新的可编程高速I/O:

–单端:GTL、GTL+、PECL、SSTL3/2(I级和II级)、HSTL(I、III、IV级)、ZBT和DDR。

–双端:LVDS、总线LVDS和LVPECL。可编程(开/关)内部并联终端(100

Ω)也支持这些I/O。

•复用I/O信号的新功能:

–输入和输出上的新DDR,速率高达350 MHz(700 MHz有效速率)。

–每个I/O新增2倍和4倍的下行链路和上行链路功能(即,50 MHz内部到200 MHz I/O)。

•增强型双块可编程功能单元(PFU):

–每个PFU八个16位查找表(LUT)。

–每个PFU有九个用户寄存器,每个LUT后面有一个,组织起来允许两个半字节独立运行,另外还有一个用于算术运算。

–每个PFU中的新寄存器控制具有两个独立的可编程时钟、时钟启用、本地SET/RESET和数据选择。

–新LUT结构允许LUT4、LUT5、新LUT6、4的灵活组合→ 1 MUX,新8→ 1 MUX和相同PFU中的纹波模式算术函数。

–每个PFU 32 x 4 RAM,可配置为单端口或双端口。使用补充逻辑和互连单元(SLIC)解码器作为存储体驱动器,创建大型快速RAM/ROM块(仅8个PFU中的128 x 8)。

–软连线LUT(SWL)允许通过快速内部路由在单个PFU中快速级联多达三个级别的LUT逻辑,从而减少路由拥塞并提高速度。

–通过路由灵活快速访问PFU输入。

–快速进位逻辑和路由到所有四个相邻的PFU,用于半字节宽、字节宽或更长的算术函数,可选择注册PFU进位。