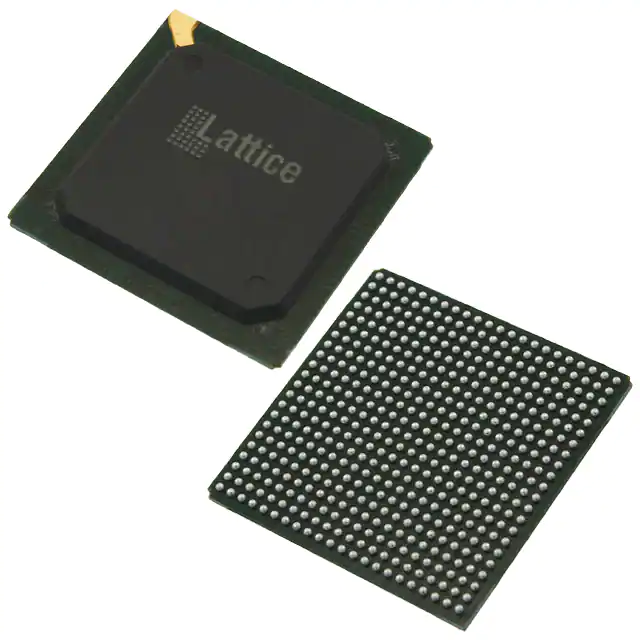

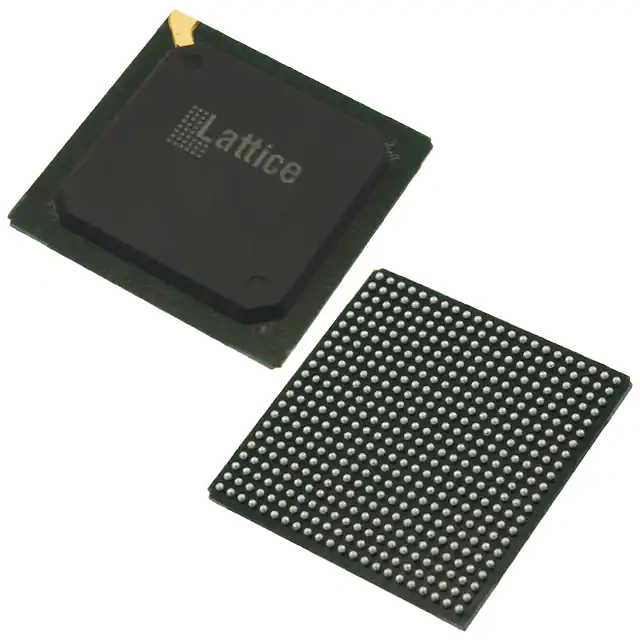

现场可编程芯片上系统(FPSC)为可编程逻辑带来了全新的维度:现场可编程门阵列(FPGA)逻辑和单个设备上的嵌入式系统解决方案。莱迪思为需要基于FPGA的设计实现的许多优点以及高速串行背板数据传输的设计人员开发了一种解决方案。ORT8850系列基于4系列可重构嵌入式片上系统(SoC)架构,由包含8个信道的背板收发器(SERDES)组成,每个信道的工作速度高达850 Mbit/s(当使用所有8个信道时为6.8 Gbit/s)。这与全双工同步接口相结合,标准单元逻辑中内置时钟和数据恢复(CDR),以及超过600K的可用FPGA系统门(ORT8850H)。随着协议和访问逻辑的增加,如独立于协议的成帧器、异步传输模式(ATM)成帧器,SONET上的分组(PoS)接口,以及用于因特网协议(IP)的HDLC成帧器等,设计者可以构建一个可配置的接口,保留经验证的背板驱动器/接收器技术。设计人员还可以使用该设备在非SONET/SDH系统内的总线上驱动高速数据传输。例如,设计者可以使用我们的PCI软核构建6.8 Gbit/s的PCI到PCI半桥。

ORT8850系列提供无时钟高速接口,用于板上或背板上的设备间通信。ORT8850的内置时钟恢复允许更高的系统性能,更容易在多板系统中设计时钟域,并且背板上的信号更少。网络设计者将受益于作为网络终端设备的背板收发器。背板收发器提供数据的SONET加扰/解扰,简化SONET成帧、指针移动和传输开销处理,以及将网络终止到专有系统的可编程逻辑。对于非SONET应用程序,所有SONET功能都对用户隐藏,不需要事先的网络知识。

特色

嵌入式核心功能

•在ORCA系列4 FPGA中实现。

•允许广泛的高速背板应用,包括SONET传输和终端。•一般应用中不需要SONET/SDH知识。只需提供数据、78MHz-106MHz时钟和帧脉冲。

•高速接口(HSI)功能,用于无外部时钟的时钟/数据恢复串行背板数据传输。

•八通道HSI功能为每个通道提供850 Mbit/s串行接口,总芯片带宽为6.8 Gbit/s(全双工)。

•HSI功能使用莱迪思的850 Mbit/s串行接口核心。支持从126 Mbit/s到850 Mbit/s的速率。

•符合EIA®-644的LVDS I/O支持热插拔。所有嵌入式LVDS I/O均包括输入和输出板上终端,以实现背板的长距离驱动。

•低功耗1.5 V HSI核心。

•低功耗LVDS缓冲器。

•可编程STS-3和STS-12框架。

•每个四通道独立的STS-3和STS-12数据流。

•8:1数据复用/解复用,用于FPGA逻辑中106.25 MHz字节宽的数据处理。

•片上锁相环(PLL)时钟符合ITU-T建议G.958的(B类)抖动容限规范。

•基于每个信道的HSI接收机断电选项。

•一旦其参考时钟恢复到正常操作状态,HSI自动从时钟丢失中恢复。

•多个ORT8850设备之间的帧对齐,以OC-192/STM-64及以上速率进行工作/保护切换。

•通过传输开销提取/插入进行带内管理和配置。

•支持仅插入A1/A2帧字节或不插入字节的透明模式。

•简化的指针处理器(指针移动器),用于8 kHz帧与系统时钟对齐。

•内置边界扫描(IEEE®1149.1 JTAG)。

•FIFO将所有八个信道(两组四个信道或四组两个信道)的输入数据对齐,用于两个SONET加扰。可选的绕过对准FIFOs的能力。

•1+1保护通过保护的软件或硬件控制支持STS-12/STS-48冗余

开关应用。通过多个设备支持STS-192及以上费率。

•ORCA FPGA软知识产权核心支持多种应用。

•可编程同步传输模块(STM)指针移动器旁路模式。

•可编程STM成帧器旁路模式。

•可编程时钟和数据恢复(CDR)旁路模式(时钟LVDS高速接口)。

•CDR I/O的冗余输出和多路复用冗余输入允许在单个设备上实现具有冗余的八个信道。

FPGA功能

•高性能平台设计:

–0.16µm 7级金属技术。

–内部性能>250 MHz。

–超过600K FPGA系统门(ORT8850H)。

–符合多个I/O接口标准。

–1.5 V操作(功率比1.8 V操作低30%)可提高性能。

•传统I/O选择:

–LVTTL(3.3V)和LVCMOS(2.5V和1.8V)I/O。

–每引脚可选I/O箝位二极管提供3.3 V PCI合规性。

–单独可编程驱动能力:24 mA汇点/12 mA源、12 mA汇点/6 mA源或6 mA汇点/3 mA源。

–支持两种转换速率(快速和转换受限)。

–快速捕获输入锁存器和输入触发器/锁存器,减少输入设置时间和零保持时间。

–快速开式排水驱动能力。

–能够注册三态启用信号。

–芯片外时钟驱动能力。

–输出路径中的两个输入函数发生器。

•新的可编程高速I/O:

–单端:GTL、GTL+、PECL、SSTL3/2(I级和II级)、HSTL(I、III、IV级)、ZBT和DDR。

–双端:LVDS、总线LVDS、LVPECL。

–LVDS包括每个I/O和片上参考生成的可选片上终端电阻器。

•复用I/O信号的新功能:

–输入和输出均采用新的双倍数据速率(DDR),速率高达350 MHz(700 Mbit/s有效速率)。

–每个I/O新增2倍和4倍的下行链路和上行链路功能(即,50 MHz内部到200 MHz I/O)。

•增强型双四可编程功能单元(PFU):

–每个PFU八个16位查找表(LUT)。

–每个PFU有九个用户寄存器,每个LUT后面有一个,组织起来允许两个半字节独立运行,另外还有一个用于算术运算。

–每个PFU中的新寄存器控制具有两个独立的可编程时钟、时钟启用、本地SET/RESET和数据选择。

–新LUT结构允许LUT4、LUT5、新LUT6、4的灵活组合→ 1 MUX,新8→ 1 MUX和相同PFU中的纹波模式算术函数。

–每个PFU 32 x 4 RAM,可配置为单端口或双端口。使用SLIC解码器作为存储体驱动器,创建大型快速RAM/ROM块(仅8个PFU中的128 x 8)。

–软连线LUT(SWL)允许通过快速内部路由在单个PFU中快速级联多达三个级别的LUT逻辑,从而减少路由拥塞并提高速度。

–通过路由灵活快速访问PFU输入。

–快速进位逻辑和路由到所有四个相邻的PFU,用于半字节宽、字节宽或更长的算术函数,可选择注册PFU进位。

•丰富的高速缓冲和非缓冲路由资源比以前的架构提供了2倍的平均速度改进。

•使用专用路由资源,为本地和全局路由优化分层路由。这将导致

更快的路由时间和可预测的高效性能。

•SLIC在每个可编程逻辑单元中提供八个三态缓冲器、最多10位解码器和PAL®型“与或反相”(AOI)。

•通过双输出可编程锁相环(PPLL)改进内置时钟管理,为相位、频率和占空比(从15 MHz到420 MHz)提供最佳时钟修改和调节。可以将输入频率相乘至64x,并将输入频率分频至1/64x。