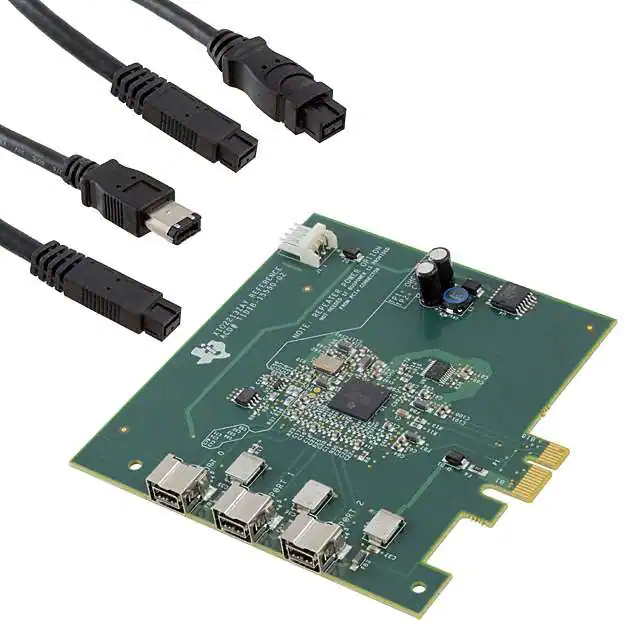

TI XIO2213BEVM是PCIe到PCI转换桥,其中PCI总线接口内部连接到具有3端口1394b PHY的1394b开放主机控制器/链路层控制器。PCIe到PCI转换桥与PCI Express到PCI/PCI-X桥规范1.0版完全兼容。此外,该桥支持标准的PCI到PCI桥编程模型。1394b OHCI控制器功能与IEEE Std 1394b和最新的1394开放式主机控制器接口(OHCI)规范完全兼容。

XIO2213BEVM同时支持四个已过帐的写入事务、四个未过帐的事务和四个未完成的事务,这些事务在任何时候都在每个方向上挂起。每个已发布的写入数据队列和完成数据队列最多可存储8K字节的数据。非端口数据队列最多可存储128字节的数据。

PCIe接口支持在每个方向上同时以250 Mbit/s的数据包吞吐量运行的×1链路。此外,桥接器支持高级错误报告功能,包括PCI Express基本规范1.1版中定义的ECRC。需要补充固件或软件来充分利用这两个功能。

实现了健壮的流水线架构,以最小化系统延迟。如果检测到奇偶校验错误,则上游和下游操作都支持数据包中毒。

PCIe电源管理(PM)功能包括活动状态链路PM、PME机制和所有常规PCI D状态。如果启用了活动状态链路PM,则链路在空闲时使用L0和L1状态自动省电。支持PM活动状态NAK、PM PME和PME到ACK消息。该桥符合最新的PCI总线电源管理规范,并提供多种低功耗模式,使主机电源系统能够进一步降低功耗

八个通用输入和输出(GPIO),通过访问PCIe配置空间进行配置,允许进一步的系统控制和定制。

提供深FIFO以缓冲1394数据并适应大的主机总线延迟。该设备为SBP-2性能提供物理写日志和高度优化的物理数据路径。该设备能够以100Mbit/s、200Mbit/s、400M bit/s和800M bit/s的速度在PCIe总线和1394总线之间传输数据。该设备提供三个1394端口,它们具有独立的电缆偏置(TPBIAS)。

根据1394开放主机控制器接口(OHCI)规范的要求,内部控制寄存器是内存映射的,不可刷新。此配置标头通过PCIe指定的配置周期访问,并提供即插即用(PnP)兼容性。

PHY提供在基于电缆的1394网络中实现3端口节点所需的数字和模拟收发器功能。每个电缆端口包含两个差分线路收发器。收发器包括根据需要监视线路状况的电路,以确定连接状态、初始化和仲裁以及分组接收和传输。提供了可选的外部2线串行EEPROM接口,以加载1394结构的全局唯一ID。

XIO2213BEVM需要外部98.304MHz晶体振荡器来生成参考时钟。外部时钟驱动内部锁相环(PLL),该锁相环产生所需的参考信号。该参考信号提供控制出站编码信息的传输的时钟信号。当通过断言PD端子为高而启用掉电(PD)功能时,停止PLL的操作。要通过电缆端口传输的数据位被内部锁存、串行组合、编码,并以98.304、196.608、393.216、491.52或983.04Mbit/s(分别称为S100、S200、S400、S400B或S800速度)作为出站信息流传输。

为了确保XIO2213BEVM符合IEEE Std 1394b-2002,必须断言BMODE终端。BMODE终端不选择电缆接口操作模式。BMODE选择内部PHY段/LLC段接口操作模式,并影响电缆上的仲裁模式。正常操作期间,BMODE必须拉高。

三个包终端用作输入,以设置自ID包中三个配置状态位的默认值。根据设备设计,可通过1-k电阻器将其拉高或通过硬接线将其拉低。PC0、PC1和PC2端子指示节点的默认电源等级状态(需要电缆供电或向电缆供电的能力)。PHY寄存器集中的竞争者位指示节点是同步资源管理器(IRM)或总线管理器(BM)的竞争者。在XIO2213B上,该位只能通过写入PHY寄存器集来设置。如果节点要成为IRM或BM的竞争者,则节点软件必须在PHY寄存器集中设置此位。

特色

- 全×1 PCI Express(PCIe)吞吐量

- 完全符合PCI Express基本规范1.1版

- 利用100 MHz差分PCI Express公共参考时钟或125 MHz

单端参考时钟 - 完全支持IEEE标准P1394b-2002的规定

- 完全符合IEEE标准1394-1995的高性能规定

串行总线和IEEE标准1394a-2000 - 完全符合1394开放主机控制器接口(OHCI)规范,

1.1版和1.2版草案 - 100M Bit/s、200M Bit/s和400M的三个IEEE Std 1394b完全兼容电缆端口

Bit/s和800M Bit/s - 电缆端口监控与远程节点的活动连接的线路状况

- 电缆电源状态监测

- EEPROM配置支持加载1394结构的全局唯一ID

- 支持D1、D2、D3hot

- 活动状态链路电源管理在

PCI Express链路空闲,同时使用L0和L1状态 - 八个3.3-V多功能通用I/O(GPIO)端子