XIO1100ZGBR是PCI Express。符合PCI Express基本规范修订版1.1的PHY,并通过使用PCI Express的PHY接口中描述的接口的修改版本将PCI Express媒体访问层(MAC)连接到PCI Express串行链路。Intel Corporation的体系结构(也称为PIPE接口)。在本数据手册中,PIPE接口的修改版本称为TI-PIPE接口。

TI-PIPE接口是引脚可配置接口,可配置为16位或8位接口。

- 16位TI-PIPE接口是具有由RXCLK输出时钟计时的16位输出总线(RXDATA)和由TXCLK输入时钟计时的十六位输入总线(TXDATA)的125MHz 16位并行接口。两条总线都使用单数据速率(SDR)时钟进行计时,其中数据转换位于相关时钟的上升沿。

- 8位TI-PIPE接口是250MHz 8位并行接口,具有由RXCLK输出时钟计时的8位输出总线(RXDATA)和由TXCLK输入时钟计时的八位输入总线(TXDATA)。两条总线都使用双倍数据速率(DDR)时钟进行计时,其中数据转换在时钟的上升沿和下降沿。

XIO1100ZGBR PHY通过传输差分对(TXP和TXN)和接收差分对对(RXP和RXN)连接到2.5 Gbps PCI Express串行链路。XIO1100ZGBR PHY接收差分对(RXP和RXN)的输入数据通过RXDATA输出总线转发到MAC。在TXDATA输入总线上从MAC接收的数据被转发到XIO1100ZGBR PHY传输差分对(TXP和TXN)。

XIO1100ZGBR还负责处理输出数据的8B/10B编码/解码和加扰/解扰。此外,XIO1100ZGBR可以根据使用8B/10B机制保证的转换恢复/内插接收器侧的时钟,并将其提供给数据链路层逻辑的接收侧。

除了TI-PIPE接口之外,XIO1100ZGBR还具有一些TI专有的边带信号,一些客户可能希望使用这些信号来利用额外的XIO1100ZHGBR低功耗状态功能(例如,在L1电源状态期间禁用PLL)。

特色

- X1 PCI Express串行链路

- PCI Express 1.1兼容

- 可选参考时钟(100 MHz、125 MHz)

- 低功耗能力

- TI-PIPE MAC接口

- 源同步TX和RX端口

- 125 MHz TX/RX时钟

- 可选16位SDR或8位DDR模式

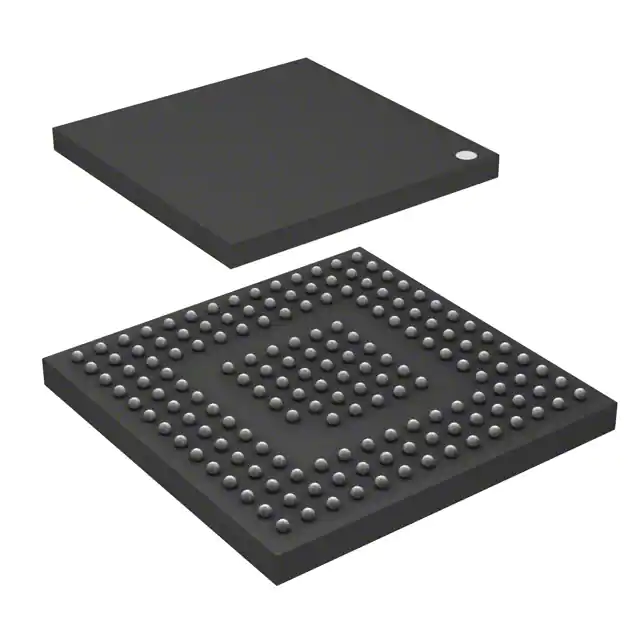

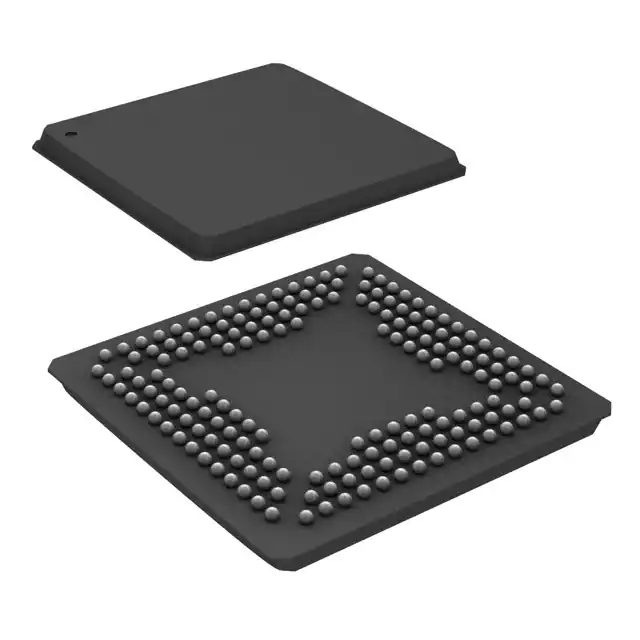

- 100针MicroStar BGA封装

- 可选1.5-V或1.8V LVCMOS缓冲器。