• High performance

• Easy BGA package features

– 100ns initial access for 512Mb, 1Gb Easy BGA

– 105ns initial access for 2Gb Easy BGA

– 25ns 16-word asynchronous page read mode

– 52 MHz (Easy BGA) with zero WAIT states and 17ns clock-to-data output synchronous burst read mode

– 4-, 8-, 16-, and continuous word options for burst mode

• TSOP package features

– 110ns initial access for 512Mb, 1Gb TSOP

• Both Easy BGA and TSOP package features

– Buffered enhanced factory programming (BEFP) at 2 MB/s (TYP) using a 512-word buffer

– 1.8V buffered programming at 1.46 MB/s (TYP) using a 512-word buffer

• Architecture– MLC: highest density at lowest cost

– Symmetrically blocked architecture (512Mb, 1Gb, 2Gb)

– Asymmetrically blocked architecture (512Mb, 1Gb); four 32KB parameter blocks: top or bottom configuration

– 128KB main blocks

– Blank check to verify an erased block

• Voltage and power

– VCC (core) voltage: 1.7–2.0V

– VCCQ (I/O) voltage: 1.7–3.6V

– Standby current: 70µA (TYP) for 512Mb; 75µA (TYP) for 1Gb

– 52 MHz continuous synchronous read current: 21mA (TYP), 24mA (MAX)

• 16-bit wide data bus

• Security

– One-time programmable register: 64 OTP bits, programmed with unique information from Micron; 2112 OTP bits available for customer programming

– Absolute write protection: VPP = VSS

– Power-transition erase/program lockout

– Individual zero-latency block locking

– Individual block lock-down

– Password access

• Software

– 25μs (TYP) program suspend

– 25μs (TYP) erase suspend

– Flash Data Integrator optimized

– Basic command set and extended function interface (EFI) command set compatible

– Common flash interface

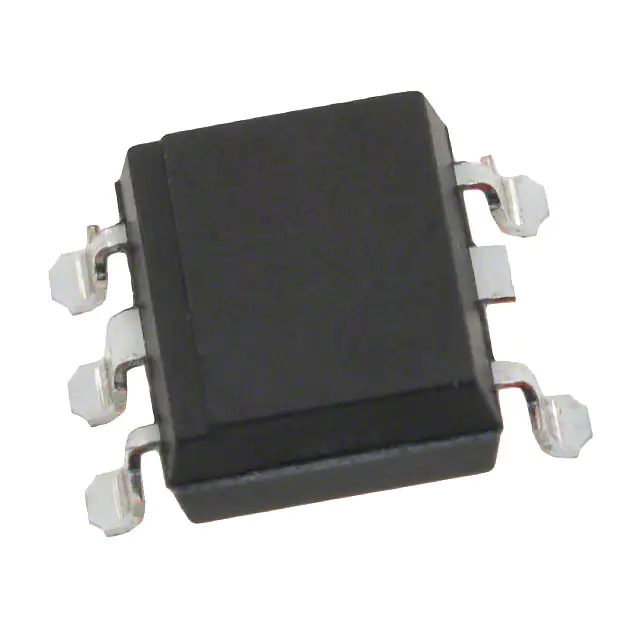

• Density and packaging

– 56-lead TSOP package (512Mb, 1Gb)

– 64-ball Easy BGA package (512Mb, 1Gb, 2Gb)

• Quality and reliability

– JESD47 compliant

– Operating temperature: –40°C to +85°C

– Minimum 100,000 ERASE cycles per block

– 65nm process technology

General Description

The Micron Parallel NOR Flash memory is the latest generation of Flash memory devices. Benefits include more density in less space, high-speed interface device, and support for code and data storage. Features include high-performance synchronous-burst read mode, fast asynchronous access times, low power, flexible security options, and three industry-standard package choices. The product family is manufactured using Micron 65nm process technology.

The NOR Flash device provides high performance at low voltage on a 16-bit data bus. Individually erasable memory blocks are sized for optimum code and data storage.

Upon initial power up or return from reset, the device defaults to asynchronous pagemode read. Configuring the read configuration register enables synchronous burstmode reads. In synchronous burst mode, output data is synchronized with a user-supplied clock signal. A WAIT signal provides easy CPU-to-flash memory synchronization.

In addition to the enhanced architecture and interface, the device incorporates technology that enables fast factory PROGRAM and ERASE operations. Designed for low-voltage systems, the devIce supports READ operations with VCC at the low voltages, and ERASE and PROGRAM operations with VPP at the low voltages or VPPH. Buffered enhanced factory programming (BEFP) provides the fastest Flash array programming performance with VPP at VPPH, which increases factory throughput. With VPP at low voltages, VCC and VPP can be tied together for a simple, ultra low-power design. In addition to voltage flexibility, a dedicated VPP connection provides complete data protection when VPP ≤ VPPLK.

A command user interface is the interface between the system processor and all internal operations of the device. The device automatically executes the algorithms and timings necessary for block erase and program. A status register indicates ERASE or PROGRAM completion and any errors that may have occurred.

An industry-standard command sequence invokes program and erase automation. Each ERASE operation erases one block. The erase suspend feature enables system software to pause an ERASE cycle to read or program data in another block. Program suspend enables system software to pause programming to read other locations. Data is programmed in word increments (16 bits).

The protection register enables unique device identification that can be used to increase system security. The individual block lock feature provides zero-latency block locking and unlocking. The device includes enhanced protection via password access; this new feature supports write and/or read access protection of user-defined blocks. In addition, the device also provides the full-device OTP security feature.

(Picture:Pinout / Diagram)