■ Integrated, ultra low power SRAM, power-fail control circuit, and battery

■ Conventional SRAM operation; unlimited WRITE cycles

■ 10 years of data retention in the absence of power

■ Battery internally isolated until power is first applied

■ Automatic power-fail chip deselect and WRITE protection

■ WRITE protect voltages:

(VPFD = power-fail deselect voltage)

– M48Z128: VCC = 4.75 to 5.5 V;

4.5 V ≤ VPFD ≤ 4.75 V

– M48Z128Y: VCC = 4.5 to 5.5 V;

4.2 V ≤ VPFD ≤ 4.5 V

■ Pin and function compatible with JEDEC standard 128 K x 8 SRAMs

■ RoHS compliant

– Lead-free second level interconnect

Description

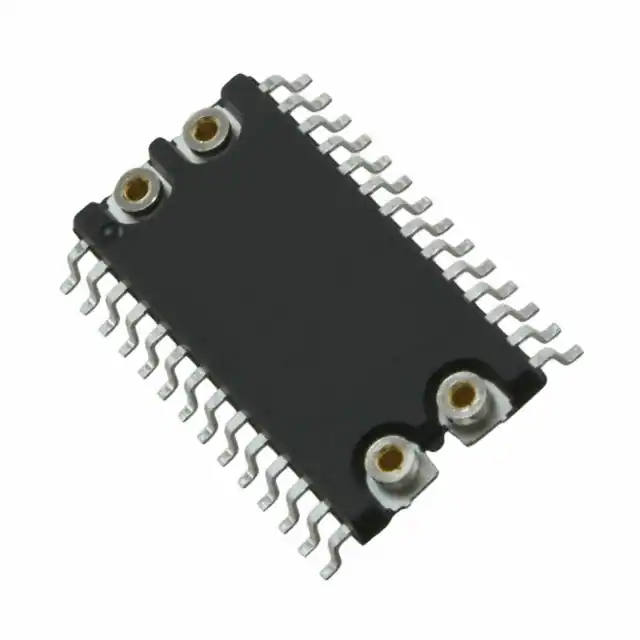

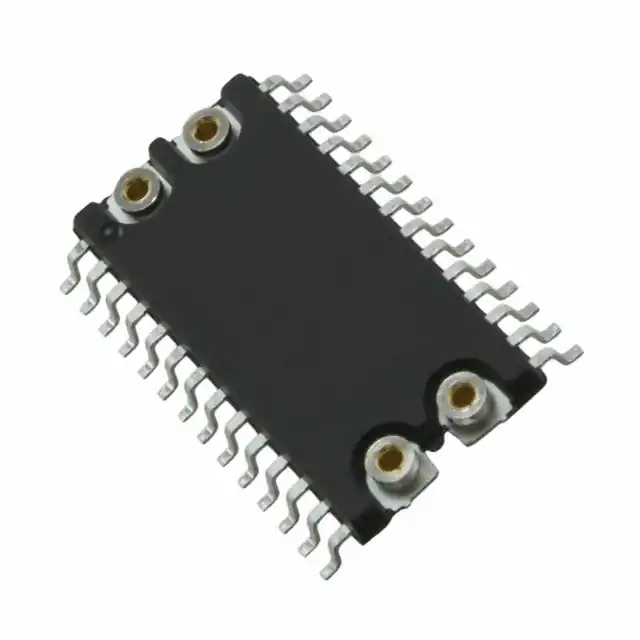

The M48Z128/Y ZEROPOWER® RAM is a 128 Kbit x 8 non-volatile static RAM organized as131,072 words by 8 bits. The device combines an internal lithium battery, a CMOS SRAM and a control circuit in a plastic, 32-pin DIP module to provide a highly integrated batterybacked memory solution.

The M48Z128/Y is a non-volatile pin and function equivalent to any JEDEC standard 128 K x 8 SRAM. It also easily fits into many ROM, EPROM, and EEPROM sockets, providing the non-volatility of PROMs without any requirement for special WRITE timing or limitations on the number of WRITEs that can be performed. The 32-pin, 600 mil DIP module houses the M48Z128/Y silicon with a long-life lithium button cell in a single package.

Feature

- Integrated,ultralowpowerSRAMandpower-failcontrolcircuit

- UnlimitedWRITEcycles

- READcycletimeequalsWRITEcycletime

- Automaticpower-failchipdeselectandWRITEprotection

- WRITEprotectvoltages(VPFD=power-faildeselectvoltage):

- M48Z02:VCC=4.75to5.5V;4.5V≤VPFD≤4.75V

- M48Z12:VCC=4.5to5.5V;4.2V≤VPFD≤4.5V

- Self-containedbatteryintheCAPHATDIPpackage

- PinandfunctioncompatiblewithJEDECstandard2Kx8SRAMs

- RoHScompliant

- Lead-freesecondlevelinterconnect

(Picture: Pinout)