德国研究人员设计了一种检测芯片操纵的新方法

德国研究人员开发了一种新方法,可以在生产过程的早期检测微芯片中的硬件操作,此时芯片最容易受到攻击。2023年4月1日作者:Shraddha Tupe

攻击者不仅可以在软件中,还可以在硬件中制造安全漏洞。为了解决这个问题,德国研究人员最近设计了一种检测微芯片硬件操作的新方法。这种操作最有可能发生在芯片的生产过程中,此时它们最容易受到攻击。因为这些小改动设计得不显眼,所以制造商往往不会发现它们。

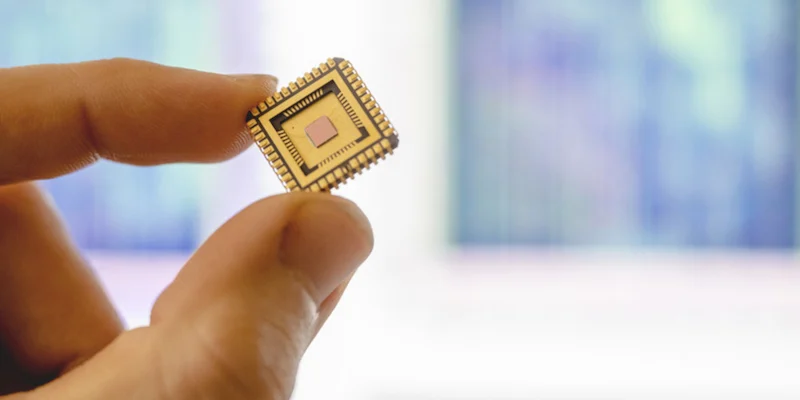

实验中评估的一个微芯片。研究人员检查了两平方毫米大小的芯片。图片由波鸿鲁尔大学提供

硬件特洛伊木马是对电子芯片电路进行的物理或行为修改,使攻击者能够控制技术应用程序。这种硬件攻击可能会造成严重后果,造成部分电信基础设施的损坏甚至瘫痪。检测这些变化对于确保基于微芯片的设备的安全性和可靠性很重要。

研究人员对显微镜和算法进行研究

德国波鸿鲁尔大学和波鸿马克斯·普朗克安全与隐私研究所(MPI-SP)的研究人员开发了一种技术,使用电子显微镜图像和检测算法来识别制造芯片的施工计划中的偏差。

研究人员建议制造商将收到的半导体器件与最初提交给铸造厂的设计文件进行比较。虽然该团队认识到,这种比较需要合格的专家和先进的实验室设备,但它将保护数千台设备的数据隐私。

为了测试他们的检测方法,研究人员分成两个小组:一个红色小组和一个蓝色小组。红色团队的任务是在四代现代CMOS技术(28nm、40nm、65nm和90nm)的布局中植入小的变化,作为插入硬件特洛伊木马的替代品。从那里开始,蓝色团队开始使用电子显微镜图像比较来检测制造的设备和数字布局之间的差异。

硬件特洛伊木马的捉迷藏

研究人员首先使用机械和化学方法制备了芯片,拍摄了数千张最低芯片层的图像,这些芯片层本身包含数十万个执行逻辑运算的标准单元。由于红队在芯片已经由第三方制造后无法修改,他们追溯性地更改了设计,以最大限度地减少施工计划和芯片之间的偏差。蓝色团队的工作是在不知道该寻找什么以及在哪里的情况下检测这些变化。

顶层显示了四个经过评估的ASIC的布局。在底部,你会看到芯片背面的融合SEM图像。研究人员只评估了标准单元格区域内(橙色正方形内)的偏差。图片由波鸿鲁尔大学/MPI-SP提供

通过他们的算法,蓝色团队在40例病例中检测到37例出现偏差,检测率为92.5%。研究人员在识别40nm、65nm和90nm芯片尺寸的修改方面最为成功,共有500例假阳性。该方法在检测最小28nm芯片的细微变化方面效果较差。该团队建议,通过改进检测算法,他们也可以提高这种芯片尺寸的检测率。

改进早期后门检测

如果半导体制造商采用这项技术,他们可能会通过在生产过程的早期发现弱点来提高基于微芯片的设备的安全性。然而,这种技术的一个挑战是,芯片上的杂质可能会阻碍图像特定区域的可见性。即使是微小的异物,如微小的碎片、灰尘斑点或头发,也会使整排标准细胞模糊不清,这给检测带来了重大障碍。研究人员建议在洁净的房间里使用扫描电子显微镜来提高准确性。