RISC-V峰会上披露的解决方案:安全、验证等

在今年的RISC-V峰会上,利益相关者推出了围绕验证、安全和软件定义SoC的解决方案。2022年12月15日,杰克·赫兹

本周是在加利福尼亚州圣何塞举行的年度RISC-V峰会,业内许多主要参与者齐聚一堂,分享技术,讨论RISC-V行业的未来。在2022年众多RISC-V公告的基础上,今年的峰会不乏令人兴奋的公告。

其中,Imperas、XMOS和Codasip最近发布的消息尤其令人感兴趣。在本文中,我们将研究这些版本中的每一个,以了解RISC-V行业的当前和未来方向。

Imperas RISC-V验证工具更新

来自本周RISC-V峰会的第一组消息来自Imperas关于其RISC-V验证软件的消息。

设计验证在RISC-V中尤为重要,因为该标准的开源性质意味着任何人都可以为IP做出贡献。因此,如果不仔细管理,就有可能在设计中引入错误或不一致。

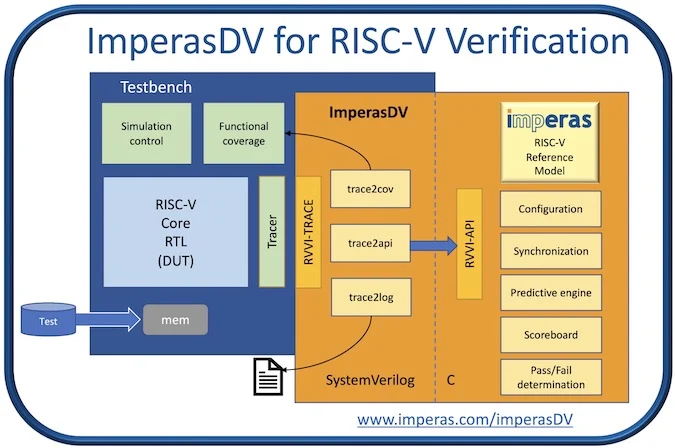

使用ImperasDV的RISC-V设计工作流程。图片由Imperas提供

为了解决这一问题,Imperas宣布对其ImperasDV软件进行一系列新的更新,这是一种领先的RISC-V设计验证软件工具。这些更新包括包含riscvISACOV IP扩展,这是一组SystemVerilog函数库,以及包含体系结构验证测试套件。

这些新的测试套件包括RV32E、RV64E、Zc和Zmmul规范,每一个规范都有助于确保硬件实现符合RISC-V软件生态系统的期望。

通过这些对ImperasDV的新添加,Imperas希望为RISC-V设计者提供可靠开发下一代RISC-V设计所需的工具和灵活性。

XMOS推出RISC-V SoC

接下来,XMOS发布了针对RISC-V的新软件定义SoC平台。具体而言,XMOS宣布,他们将在第四代xcore平台中采用RISC-V兼容架构。

xcore.ai处理器的框图。图片由XMOS提供。(点击图片放大)

XMOS向RISC-V兼容架构过渡的主要原因之一是RISC-V是一种开源技术。正因为如此,XMOS希望这一转变将为嵌入式设计师提供比闭源解决方案更多的技术优势、工具和资源。

此外,XMOS指出,向RISC-V体系结构的过渡为其设计者提供了在软件中定义整个系统的灵活性。其结果是,设计师将能够实现更快的上市时间、更大的设计差异化和更经济的整体解决方案。

RISC-V安全倡议启动

最后但并非最不重要的是,在本周的RISC-V峰会上,Codasip宣布启动一项新的RISC-V安全倡议。

在某些方面,RISC-V的安全性比其他指令集体系结构(ISA)更重要。其中一个原因是RISC-V是开源的,这意味着任何人都可以访问和修改设计。这种开放性有其优点,但也有缺点,因为如果不仔细管理设计,安全漏洞可能会更透明,更容易引入。

Codasip首席执行官Ron Black出席RISC-V峰会。图片来自Codasip的RISC-V峰会2022聚焦会议

为了解决这一问题,Codasip推出了名为SecuriC5的新举措,旨在为客户提供一个基于Codasip IP和第三方技术的安全可靠的定制计算平台。据新闻报道,这项新举措将以RISC-V国际工作组的现有工作为基础,并将在新标准获得批准后实施。

为了获得最大的可见性,从而获得最大的安全性,Codasip正在与该倡议中的一些关键行业参与者合作。具体来说,像英特尔和加密量化这样的组织是该倡议的支持者。