达到232层的峰值,是美光3D NAND的极限

美光公司的垂直分层存储器技术标志着业界最高的面密度NAND芯片。2022年7月29日,杰克·赫兹

随着5G和云计算的普及,数据和流量出现了巨大的繁荣。这种对数据的日益依赖使该行业同样依赖存储和内存技术。

然而,与半导体行业的其他领域一样,存储器行业目前需要新的架构来帮助推动技术的发展。本周,美光宣布生产其232层3D NAND技术,成为存储器行业的头条新闻。

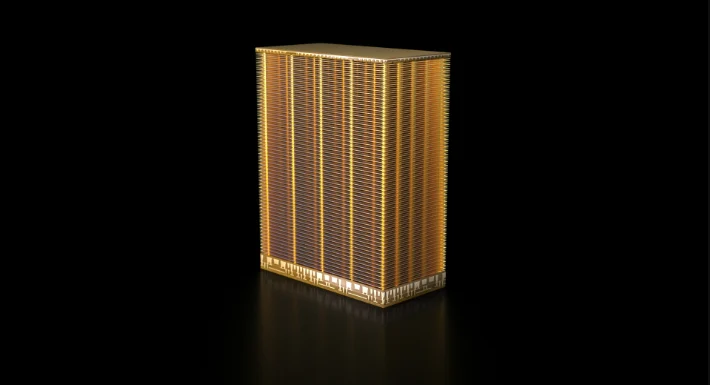

232层NAND闪存。图片由美光提供

为什么是3D NAND?

如今,NAND闪存技术在功率效率、吞吐量性能和单片芯片容量方面被推向了新的极限。由于这些前所未有的要求,传统的2D NAND闪存技术很快就过时了。

传统NAND技术的一个挑战是,单个晶体管平面上的单元之间的物理距离随着单元尺寸的减小而减小。这里的挑战是,闪存通过在单个晶体管单元内存储电压状态来工作,并且随着单元之间的距离减小,晶体管上的电流泄漏也会增加。由于这个原因,NAND闪存制造商在传统的扩展方面受到限制,无法在不牺牲性能的情况下降低到13nm以下。

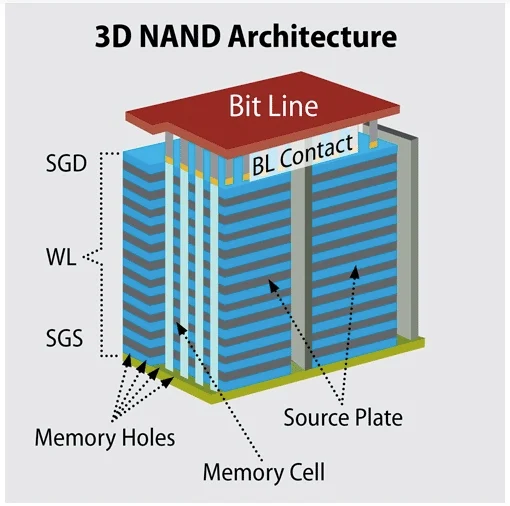

3D NAND解决方案的体系结构。图像由企业存储解决方案提供

相反,许多人已经转向3D NAND技术来不断改进NAND闪存。3D NAND指的是NAND架构,其中NAND单元垂直堆叠成彼此顶部的层,而不是传统NAND中的并排。在美光的3D NAND技术中,闪存芯片由分为块和平面的存储单元组成,其中每个单元都有连接到它们的字线,用于读/写访问。

转向3D体系结构有几个优点。最值得注意的是能够将晶体管单元彼此隔开,以避免来自相邻单元的泄漏和干扰。通过这种方式,3D NAND允许设计者在不牺牲性能的情况下增加存储器密度,这会削弱过程中连续缩放的性能限制。

Micron堆叠232层NAND

本周,美光宣布批量生产其232层3D NAND技术。

作为该公司上一代176层的后续产品,232层3D NAND技术建立在美光的CMOS阵列下(CuA)架构的基础上。在这种架构中,Micron将NAND的位单元阵列堆叠成层,以提供每平方毫米硅可能的最大数量的位。在这样做的过程中,美光的目标是尽可能实现最低的每比特成本和最大的密度。

当前NAND电容结构与美光的3D RG NAND闪存相比。图片由美光提供

得益于高层数,新的232层NAND闪存技术可以在11.5毫米x 13.5毫米的封装中为每个芯片提供高达1太比特的数据。与美光之前的176层技术相比,232层解决方案在更小28%的封装中,每面积的比特密度增加了45%。

除了密度之外,美光还声称在性能方面也有进步。美光表示,新的232层NAND设备提供了业界最高的层数、最高的面密度(bits/mm2.),最快的I/O速度为2.4 GB/s。与美光之前的176层NAND产品相比,232层6平面架构据说可以实现100%的高写带宽、75%的高读带宽和50%的传输速率提高。美光相信,在未来的嵌入式NAND解决方案中,每个芯片的这些改进将转化为更大的性能和能源收益。