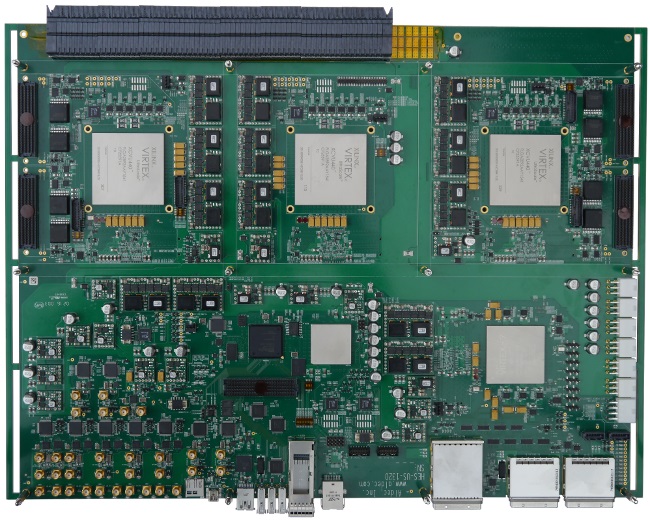

HES-US-1320–SoC/ASIC原型和仿真

带有三个Xilinx Virtex UltraScale XCVU440 FPGA的HES-US-1320板旨在实现ASIC和SoC设计的高速物理原型设计和仿真。该板提供7900万个ASIC门的容量,估计FPGA利用率为60%,可扩展至3.16亿个ASIC门。每个UltraScale FPGA模块都与DDR4 SO-DIMM连接,以支持高达48 GB的聚合内存。UltraScale设备的最高I/O计数封装和正确的板载跟踪路由确保了可靠的LVDS和GTH传输,达到FPGA设备的固有极限。一个非常精确设计的时钟块提供5条长度对齐的全局时钟线,路由到每个FPGA设备。由于集成了不同的振荡器、可编程时钟合成器和交叉点开关复用器,它还提供了多种配置选项。该板包含本地高速通信接口,如PCIe第3代、USB 3.0、1 Gb以太网、QSFP+、SATA和FMC-HPC连接器,以实现可扩展性。

- 零件编号:他

- 设备购买:点击在这里联系客服获取相关信息!

带有三个Xilinx Virtex UltraScale XCVU440 FPGA的HES-US-1320板旨在实现ASIC和SoC设计的高速物理原型设计和仿真。该板提供7900万个ASIC门的容量,估计FPGA利用率为60%,可扩展至3.16亿个ASIC门。每个UltraScale FPGA模块都与DDR4 SO-DIMM连接,以支持高达48 GB的聚合内存。UltraScale设备的最高I/O计数封装和正确的板载跟踪路由确保了可靠的LVDS和GTH传输,达到FPGA设备的固有极限。一个非常精确设计的时钟块提供5条长度对齐的全局时钟线,路由到每个FPGA设备。由于集成了不同的振荡器、可编程时钟合成器和交叉点开关复用器,它还提供了多种配置选项。该板包含本地高速通信接口,如PCIe第3代、USB 3.0、1 Gb以太网、QSFP+、SATA和FMC-HPC连接器,以实现可扩展性。

主要功能和优点

- 与Aldec高性能模拟器Active HDL或Riviera PRO的成本效益捆绑包

- 用于加速和仿真验证模式的原型硬件重用

- 卓越的质量得到业界领先的1年保修

- 撒旦

- 质量保证计划+

- 千兆以太网

- USB 3.0接口

- 1x PCIe第3代x8

- 1x可切换PCIe第3代x16或x8代

- BPX背板连接器

- FMC HPC子卡连接器

- 时钟:5倍全局、低偏斜、长度对齐的时钟线和可配置的时钟块

- 3个DDR4 SO-DIMM

- 1x Virtex-7 XC7VX690T主机FPGA

- 3个Virtex UltraScale XCVU440主FPGA

包装物件清单 (含配件)

- 诊断测试套件

- 用于板配置和管理的HES Proto AXI软件

- HES-US-1320板,带3个Xilinx®Virtex®-UltraScale XCVU440 FPGA

- 可选HES-DVM软件,用于启用仿真和仿真加速

- 可选Proto-AXI接口,高速PCIe到AMBA AXI桥接

- 板接口参考设计