PCB线路板设计的原则,工程师免费教你,设计水平不言而喻

我们在设计PCB线路板时应该注意的问题,干货满满...

我们在设计PCB线路板时应该注意的问题,干货满满。主要有以下几方面的内容:

一、PCB电路板抗干扰设计原则

1、要选择合适的电源,它相当于人的心脏,给各个电路提供电压电流,要求纹波电压越小越好;

2、尽量加宽电源线的宽度;

3、保证电源线、地线的走向和数据线传输的方向一致;

4、使用抗干扰元器件(磁珠或者滤波电容);

5、电源入口添加去耦电容及高频滤波电容。

二、地线的设计

1、模拟地和数字地分开(用磁珠或者0欧姆无感电阻分开);

2、尽量采用单点接地;

3、尽量加宽地线的宽度(通过三倍电流的电路,大面积铺铜箔);

4、将比较敏感的电路连接到稳定的接地参考源;

5、对PCB进行分区设计,把高带宽的噪声电路与低频电路分开;

6、尽量减少接地环路的面积,降低电路的感应噪声。

三、元器件的配置

1、不能有过长的平行信号线;

2、对PCB进行分区布局;

3、考虑PCB板在材料中的位置和方向;

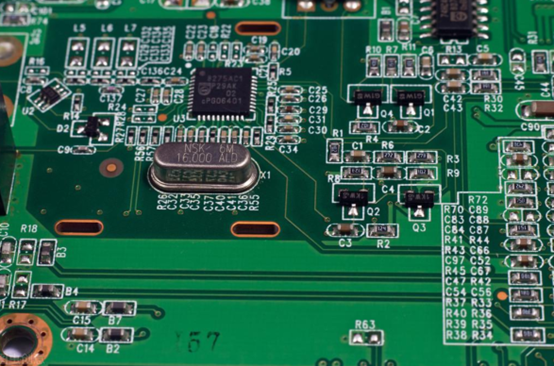

4、缩短高频元器件之间的引线;

5、保证PCB的时钟发生器(晶振)和CPU的时钟输入端尽量靠近;

6、元件应用围绕核心器件配置,尽量减少引线长度。

四、去耦电容的配置

1、每10集成电路要加一片充放电电容(10uF左右);

2、引线式电容用于低频,贴片式电容用于高频;

3、每个集成芯片要布置一个0.01uF高频瓷片电容;

4、对抗噪声能力弱,关断时电源变化的器件要加高频去耦合电容;

5、电容之间不要共用过孔,(多个过孔接地或接电源);

6、去耦合电容引脚不能太长。

五、降低噪声和电磁干扰的原则

1、尽量采用45度折线而不是90度折线;

2、用串联电阻的方法来降低电路信号的跳变速率;

3、石英晶振的外壳要接地;

4、闲置不用的门电路不要悬空;

5、时钟线垂直IO线时干扰小;

6、尽量让时钟线周围的电动势趋于零;

7、IO驱动电路尽量靠近PCB的边缘;

8、任何信号线不要形成回路;

9、高频板电容分布和电感分布不能忽略;

10、通常功率线、交流线不能和信号线布局到一块线路板上。

六、其他设计规则

1、CMOS未使用的引脚要通过电阻接地或者接电源;

2、用RC电路来吸收继电器等元件的放电电流;

3、总线上加10K的上拉电阻有助于抗干扰;

4、采用全译码有更好的抗干扰性;

5、元器件不同引脚通过10K电阻接电源;

6、总线尽量短,尽量保持一样长度;

7、两层之间的布线尽量垂直;

8、发热元件尽量避开敏感元件;

9、布线时需要加上测试点和贴片机的Mark点。

这是我平常设计的时候总结出来的规律,如果你都掌握了,在平常设计时,少走很多弯路,设计出来的PCB调试时少费劲,工作很顺利。