Feature

- Dual-Port allows simultaneous access of the same memory location

- Dual chip enables allow for depth expansion without external logic

- Easily expands data bus width to 36 bits or more using the Master/Slave select when cascading more than one device

- Busy and Interrupt Flags

- On-chip port arbitration logic

- Full on-chip hardware support of semaphore signaling between ports Fully asynchronous operation from either port

- Separate byte controls for multiplexed bus and bus matching compatibility

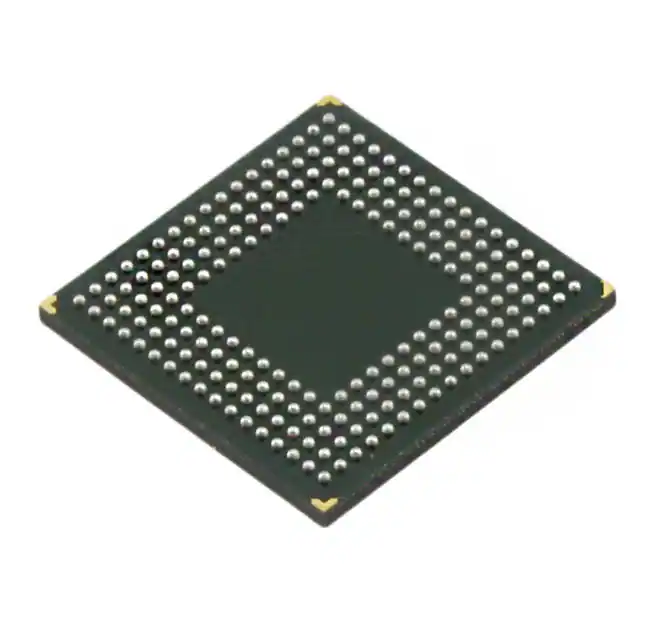

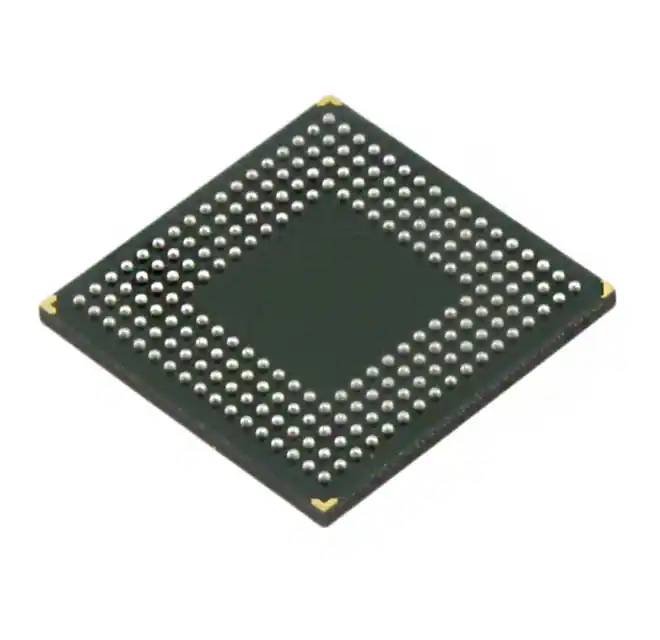

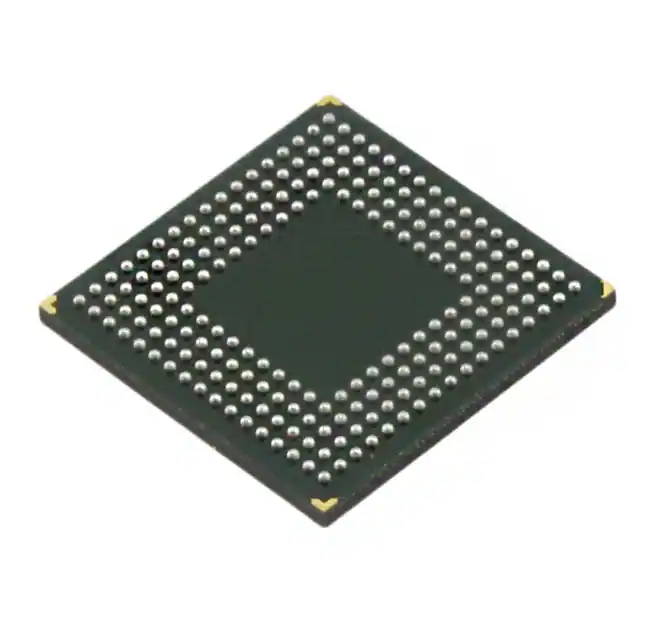

- Includes JTAG functionality on BGA package versions only

- LVTTL-compatible, single 3.3V (±150mV) power supply for core

- LVTTL-compatible, selectable 3.3V (±150mV)/2.5V (±100mV) power supply for I/Os and control signals on each port

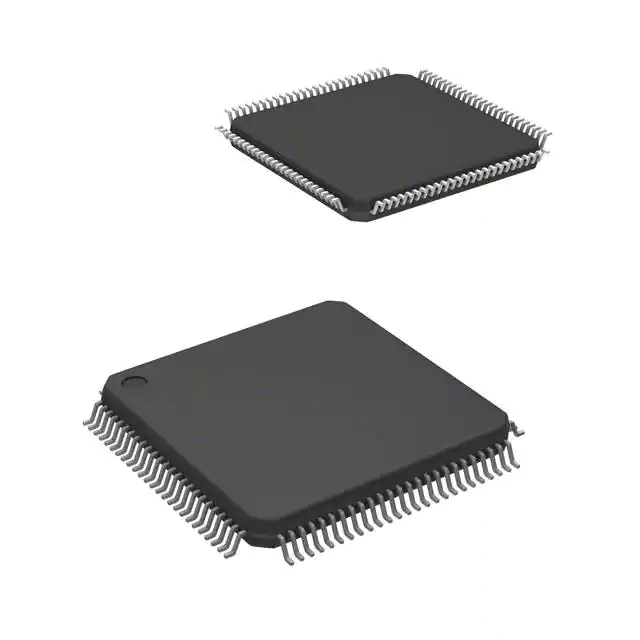

- Available in a 128-pin TQFP, 208-ball fpBGA and 256-ball BGA

- Industrial temperature range (–40C to +85C) is available