发射极耦合逻辑:作为OR/NOR门工作的电路及其应用

ECL(射极耦合逻辑)于1956年8月由Hannon S.Yourke在IBM首次发明。这种逻辑也被称为电流模式逻辑,用于IBM 7090和7094的计算机。ECL系列与数字逻辑相比速度非常快。。。

ECL(射极耦合逻辑)于1956年8月由Hannon S.Yourke在IBM首次发明。这种逻辑也被称为电流模式逻辑,用于IBM 7090和7094的计算机。ECL系列与数字逻辑系列相比速度非常快。通常,该逻辑族提供小于1ns的传播延迟。它是一个基于双极结晶体管的逻辑家族。它是可用于设计传统逻辑系统的最快逻辑族电路。本文讨论了发射极耦合逻辑电路,使用应用程序。

什么是发射器耦合逻辑?

发射极耦合逻辑是传统逻辑系统设计中使用的最好的基于BJT的逻辑家族。有时,它也被称为电流模式逻辑,这是一种非常高速的数字技术。通常,ECL被认为是最快的逻辑IC,它通过使用非常小的电压摆动来实现其高速操作,同时避免晶体管进入饱和区域。

ECL的实施方式利用正电源电压,该正电源电压被称为PECL或正参考ECL。在早期的ECL栅极中,由于抗噪声性,使用负电压电源。在那之后,正参考ECL由于其与TTL逻辑家族相比更兼容的逻辑电平而变得非常著名。

发射极耦合逻辑消耗了大量的静态功率,然而,与高频下的CMOS相比,其整体电流消耗较低。因此,ECL主要有利于时钟分配电路和基于高频的应用。

发射极耦合逻辑特性

ECL的特性将使其用于许多基于高性能的应用中。

- ECL提供两个彼此互补的输出,因为电路的操作是基于差分放大器的。

- 该逻辑族主要适用于单片制造方法,因为逻辑电平是电阻器比率的函数。

- ECL系列的器件在不使用任何外部反相器的情况下产生所提出功能的正确和互补输出。因此,它减少了封装数量和功率需求,也减少了因时间延迟而出现的问题。

- 差分放大器设计中的ECL器件提供了广泛的性能灵活性,因此ECL电路既可以用作数字电路,也可以用作线性电路。

- ECL栅极的设计通常具有高和低输入阻抗,这极有利于获得大的扇出和驱动能力。

- ECL器件在电源上产生恒定电流漏极,以简化电源的设计。

- 包括开射极输出的ECL器件简单地允许它们包括传输线驱动容量。

发射极耦合逻辑电路

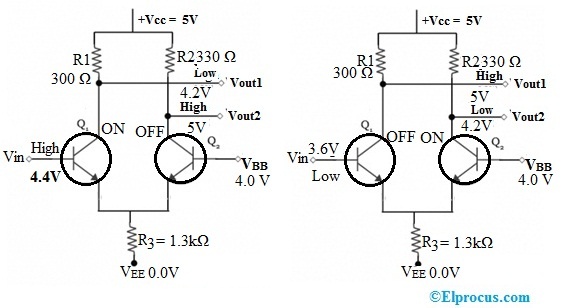

反相器的发射极耦合逻辑电路如下所示,该电路由电阻器和晶体管设计。在该电路中,两个晶体管的发射极端子简单地连接到限流电阻RE,该限流电阻用于避免晶体管进入饱和。这里,晶体管的输出取自集电极端子,而不是发射极端子。该电路提供两个输出Vout(反相输出)和Vout2(非反相输出)以及像Vin这样的输入端子,其中给出高或低输入+Vcc=5V。

发射极耦合逻辑是如何工作的?

发射极耦合逻辑的操作是,无论何时向ECL电路提供HIGH输入,它都会使“Q1”晶体管导通,Q2晶体管截止,但Q1晶体管未饱和。因此,这将把VOUT2输出拉到高电平,并且由于R1内的下降,VOUT1输出的值将是低电平。

类似地,当给ECL的VIN值为低时,它将使Q1晶体管截止,Q2晶体管导通。因此,Q2晶体三极管不会进入饱和状态。因此,它将使VOUT1输出被拉高,并且由于R2电阻内的下降,VOUT2输出值将为低。

让我们看看当施加电压时晶体管Q1和Q2是如何导通和截止的。

该电路中的两个晶体管(如Q1和Q2)通过公共发射极电阻器连接为差分放大器。

该示例电路的电压源为VCC=5.0,VBB=4.0和VEE=0V。输入的HIGH和LOW电平值简单地定义为4.4V和3.6V。实际上,该电路产生的LOW输出和HIGH电平高0.6伏;然而,这是在实际的ECL电路中进行校正的。

一旦Vin为HIGH,则Q1晶体管导通,但未饱和,Q2晶体管关断。因此,像VOUT2这样的输出电压通过R2电阻器被拉到5V,可以看出R1电阻器两端的电压降约为0.8V,因此VOUT1=4.2V(LOW)。此外,当晶体管Q1完全导通时,VE=VOUT1–VQ1=>4.2V–0.4V=3.8V。

一旦Vin为LOW,Q2晶体管将导通,但不饱和,Q1晶体管将截止。因此,使用R1电阻器将VOUT1拉至5.0 V,可以看出VOUT2为4.2 V。此外,当晶体管Q2导通时,VE=>VOUT2–VQ2=>4.2V–0.8V=>3.4V。

在ECL中,两个晶体管永远不会饱和,因为t输入/输出电压波动相当小,比如0.8v并且输入阻抗高而输出电阻低。这有助于ECL以较小的传播延迟时间更快地工作。

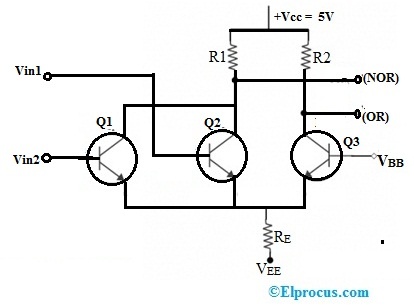

双输入发射极耦合逻辑“或非”门电路

两输入发射极耦合的逻辑OR/NOR门电路如下所示。该电路是通过对上述逆变电路的修改而设计的。修改是通过在输入侧添加一个额外的晶体管。

这个电路的工作非常简单。当施加在Q1和Q2晶体管上的输入均为低时,将使输出1(Vout1)为高值。因此,该Vout1对应于NOR门的输出。

同时,如果Q3晶体管导通,那么它将使第二输出(Vout2)为高电平。因此,该Vou2输出对应于OR门输出。

以同样的方式,如果Q1和Q2晶体管的输入都是高电平,那么它将导通Q1和Q3晶体管,并在VOUT1端子处提供低输出。

如果Q3晶体管在整个操作过程中被关断,那么它将在VOUT2端子处提供高输出。因此,下面给出了“或非”门的真值表。

| 输入 |

输入 | 或 | 也不 |

| A. |

B | Y | Y |

| 0 |

0 | 0 | 1. |

| 0 |

1. | 1. | 0 |

| 1. | 0 | 1. | 0 |

| 1. | 1. | 1. | 0 |

发射极耦合逻辑特性

ECL的特点包括以下几点。

- 与TTL相比,ECL具有更快的传播时间,范围从0.5到2ns。但是,与类似30mW的TTL相比,发射极耦合逻辑功耗更高。

- ECL的I/O电压具有类似0.8的小摆动。

- ECL的输入阻抗高,输出电阻低;因此,晶体管的状态变化非常快。

- ECL扇出容量高,栅极延迟低。

- ECL的o/p逻辑从LOW状态变为HIGH状态,但这些状态的电压电平将在TTL&EC之间变化。

- ECL的抗扰度为0.4V。

优点和缺点

这个射极耦合逻辑的优点下文将对此进行讨论。

- ECL的扇出为25,与TTL相比更好,与CMOS相比更低。

- ECL的平均传播延迟时间为1到4ns,与两种CMOS相比更好&

- TTL中。因此,它被称为最快逻辑族。

- 当发射极耦合逻辑门中的BJT在有源区中工作时,与所有逻辑族相比,它们具有最大的速度。

- ECL门产生互补输出。

- 电源引线中不存在电流开关尖峰。

- 输出可以联合耦合以提供有线OR功能。

- ECL的参数随温度变化不大。

- 从唯一的芯片可访问的功能数量很高。

这个射极耦合逻辑的缺点下文将对此进行讨论。

- 它具有极低的噪声裕度,即±200 mV。

- 与其他逻辑门相比,功耗较高。

- 为了与其他逻辑族接口,电平移位器是必要的。

- 扇出限制电容负载。

- 与TTL相比,ECL门是昂贵的。

- 与CMOS和TTL相比,ECL的抗噪声性最差。

应用

射极耦合逻辑的应用包括以下内容。

- 发射器耦合逻辑被用作极高速通信设备中的逻辑和接口技术,如光纤收发器接口、以太网和ATM(异步传输模式)网络。

- ECL是一个基于BJT的逻辑家族,其高速操作可以通过使用相对较小的电压摆动来实现,避免晶体管进入饱和区域。

- ECL用于制造IBM 360/91中的ASLT电路。

- ECL通过在初级和次级晶体管之间使用单端偏置i/p和正反馈来实现反相器功能,从而避免了堆叠晶体管的使用。

- ECL用于超高速电子器件。

因此,这是对发射极耦合逻辑或ECL电路、工作、特征、特性和应用的概述。与其他数字逻辑家族相比,ECL是基于BJT的速度非常快的逻辑家族。它通过使用小的电压摆动来达到最大速度运行,避免晶体管进入饱和区域。这个逻辑家族提供了令人难以置信的1ns传播延迟,并且在最新的ECL家族中,这种延迟被减少了。这里有一个问题,ECL的替代名称是什么?