什么是SISO移位寄存器:工作、真值表、电路图及其应用

通常,触发器用于存储一个数据位。如果我们想存储多个数据但是,我们需要许多触发器。因此,这组触发器被称为寄存器,用于移位位。有不同种类的。。。

通常,触发器用于存储一个数据位。如果我们想存储多个数据但是,我们需要许多触发器。因此,这组触发器被称为寄存器,用于移位位。根据应用的输入和访问的输出,有不同类型的寄存器可用,如SISO、SIPO、PISO和PIPO。如果寄存器用于移位右侧或左侧的位,则称为移位寄存器。本文讨论了移位寄存器的一种类型,即SISO寄存器或串行输入和串行输出移位寄存器。

什么是SISO移位寄存器?

术语“SISO”代表“串行输入串行输出”。SISO移位寄存器电路在其输入引脚上接受串行数据,并在其输出引脚上串行移出。在下一个位到达之前可以移出的位的数量取决于控制移位寄存器的操作的时钟信号的速度。这种类型的移位寄存器可以用作两个异步设备之间的缓冲器,这两个设备使用不同频率或相位的信号相互通信。

这个SISO移位寄存器框图其包括3-D触发器。这些FF的连接可以通过将一个触发器输出连接到下一个触发器输入来完成。因此,这些FF彼此同步,因为在每个触发器中施加相等的CLK信号。

这个移位寄存器只包括三个连接——SI(串行输入)、SO(串行输出)和CLK(时钟信号)。这里,SI确定输入进入左侧触发器,SO是从右侧触发器获得的输出和排序CLK信号。

在这种类型的移位寄存器中,可以从触发器的串行输入串行传输位。对于FF中的每个时钟信号,数据可以从一个相位传输到下一个相位。因此,我们可以从被称为串行输出的D-FF输出中按顺序获得比特。

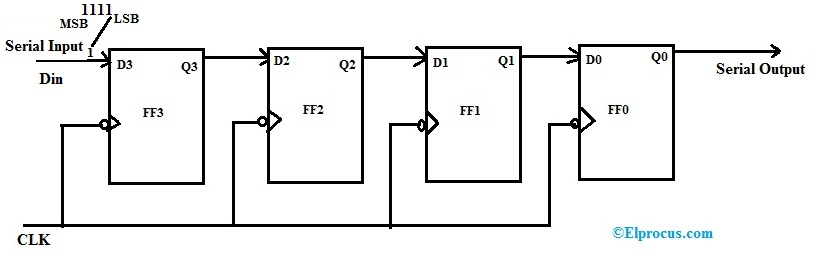

SISO移位寄存器电路图

我们知道,这种类型的移位寄存器中的输入是串行馈送的,而输出是以串行方式接收的。SISO移位寄存器电路图如下所示,其中像D0到D3这样的D FF串联连接,如下图所示。

首先,所有四个D触发器都被设置为复位模式,这样电路中的每个触发器的输出都是低电平,即“0”。

这是一个右移模式电路,这意味着当数据i/p在触发器的左端给出时,存储的位可以移到右侧以产生串行输出。现在让我们讨论给定的数据是如何存储在这个寄存器中的。

SISO移位寄存器的工作

让我们举一个1011二进制数的例子。在此之前,必须将电路设置为重置模式,以便每个寄存器的输出都是“0”,因此所有寄存器提供的输出都将是“0000”。

在像“1111”这样的4位移位寄存器示例中,LSB位为“1”,MSB位为“0”。首先,高信号(LSB位)被用作第一D3触发器的输入,然后D3=1。但主要是所有的D FF输出将为0。因此,D2=D1=D0=0。当D3输入为高信号(1)时,D3将导致“Q3”为“1”。因此,第一个下降沿的总o/p将变为1000。

类似地,当在触发器D3上给出上述4比特类高信号(1)中的下一个数据i/p比特时,这个“D3”将再次导致“Q3”为1,然而,“Q3’被作为FF“D2”的输入。因此,当所有剩余输出变为0时,这个“D2”将导致“Q2”为1。

因此,我们将获得第二个下降沿的“11”;因此将在移位寄存器中存储的位处获得“11”,因此第二下降沿的总o/p将获得o/p为“1100”。

当第三输入位状高信号(1)施加在“D3”FF时,较早的“Q2”o/p将导致“D1”i/p为“0”。这将使输出Q3、Q2和Q1为“1”,而“Q0”将为“0”。因此,第三个下降沿的总体o/p将变为“1110”。

此外,类似MSB位的高信号(1)被作为输入,之后“Q1”处的“1”将导致输入“D0”为“1”,因此,这将使“Q0”为“0”。因此,最后,SISO移位寄存器在o/p中存储1111位&。

这个SISO移位寄存器真值表如下所示。

| CLK公司 |

“Q3” | “Q2” | “Q1” | “Q0” |

| 初始(重置) | 0 |

0 | 0 | 0 |

| 1.标准时间下降边缘 |

1. | 0 | 0 | 0 |

| 2.第二次下降边缘 |

1. | 1. | 0 | 0 |

| 3.第三方下降边缘 | 1. | 1. | 1. | 0 |

| 4.第下降边缘 | 1. | 1. | 1. | 1. |

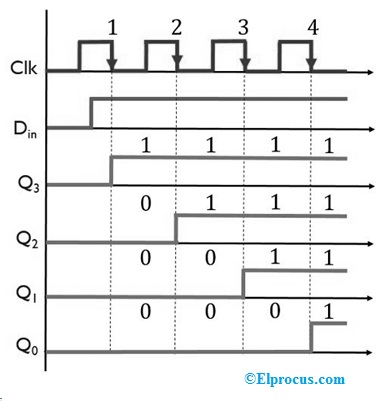

通过考虑上述真值表,SISO移位寄存器波形表示将如下所示。

在上面的波形中,第一个波形是CLK i/p信号,而第二个波形显示要存储为“1111”的数据i/p。因此,波形将是一个恒定的高信号。此外,上面所示的波形将表示FF的4个数据o/p。

首先,所有的FFs o/ps都是“0”,这在上面的波形表示中非常清楚地给出。但是,一旦第一个CLK信号到达,“Q3”输出将从“0”变为“1”,而剩余的o/ps仍为“0”。

这样,第二CLK信号“Q2”将从“0”变为“1”。因此,‘Q2’和‘Q3’将在上述波形中显示逻辑高。

SISO移位寄存器就是这样工作的。一旦第四个CLK信号到达,那么所有四个寄存器的输出将变为“1”。因此,可以通过在每个CLK信号到达时移位每个位来执行存储,因此它被称为SISO移位寄存器。

Verilog代码

这个SISO移位寄存器的verilog码如下所示。

模块sisomod(clk、clear、si、so);

输入clk、si、clear;

输出so;

注册so;

注册[3:0]tmp;

始终@(posedge clk)

开始

如果(清除)

tmp<=4’b0000;

其他的

tmp<=tmp<<1;

tmp[0]<=si;

所以=tmp[3];

终止

末端模块

应用

这个SISO移位寄存器应用s包括以下内容。

- SISO移位寄存器主要用于在数字逻辑电路中产生时间延迟。

- 这些移位寄存器用于传输操作和存储数据。

- SISO寄存器被有效地用于减少设计中连接不同系统的导线数量。

- SISO移位寄存器将每个阶段的数据延迟一个CLK时间&它们将为每个寄存器存储一个数据位。

- 这些类型的寄存器主要用于时间延迟。

因此,这一切都是关于SISO移位寄存器的概述——与应用程序一起工作。类似地使用Jk触发器的SISO移位寄存器p也可以像使用D触发器一样设计,但它需要连接J&K的两个输入。与上述基于D-FF的移位寄存器一样,在基于JK FF的移位移位寄存器中,两个输入也都在所有FF串联连接的左侧触发器处给出。这里有一个问题,什么是双向移位寄存器?