数字封装模拟子系统:实现简单模拟集成的关键?

Agile Analog开发了数字封装的模拟IP子系统,以减少SoC的设计和集成工作量。2023年5月1日作者:Darshil Patel

数字设计流程和IP块使其更容易重用和自定义不同应用程序的设计。然而,对于模拟IP块来说,情况并非如此。

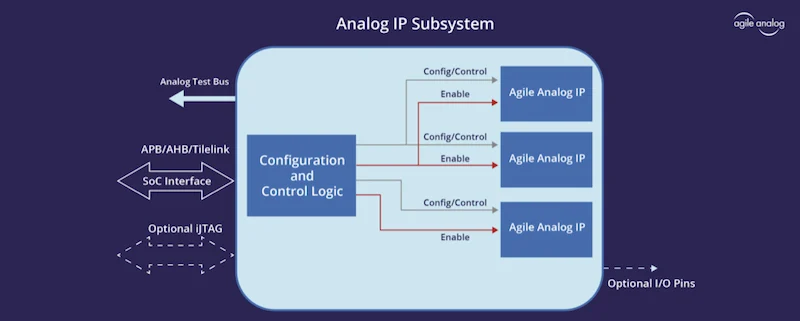

为了简化模拟IP集成,Agile analog推出了数字封装的模拟子系统,包括电源管理、PVT传感和睡眠管理。这些子系统像传统的数字IP块一样工作,允许将它们部署到数字设计流程中,并与标准接口连接。

Agile Analog数字封装IP子系统的概念

用于数字设计流程的模拟IP块

数字IP块在半导体行业中的受欢迎程度显著提高,因为数字设计流程遵循结构化和线性方法。这种方法包括定义输入和输出、逻辑门选择以及通过模拟和测试进行验证。

相反,根据模拟电路块的复杂性和参数,模拟设计流程涉及几个周期的迭代。因此,完成模拟设计所需的时间和精力都很高。复杂性也随着技术的变化而增加。另一方面,数字IP可以针对不同的技术节点进行合成或优化,而无需进行多次修改。

模拟IP对于信号处理、电源管理和RF(射频)系统仍然是必要的。在这些情况下,数字封装的模拟IP可以提供两全其美的效果。在这样的系统中,模拟电路被封装在数字控制接口中,该数字控制接口提供了控制和监测模拟行为的稳健方式。例如,数字封装的电压调节器可以包括数字控制回路,以在监测负载条件、温度和其他参数的同时改变输出功率。

敏捷模拟的新型模拟IP子系统

Agile Analog最近推出了一系列模拟子系统,以减少与模拟集成电路设计相关的上市时间、成本和工作量。

新的可定制模拟IP允许每个子系统块在覆盖数字包装的同时根据客户的要求进行定制。此外,可以针对客户特定的PDK(工艺设计工具包)修改子系统。Agile Analog声称集成IP的过程更简单,因为它消除了重复功能,减少了DRC需求,并优化了互连。该公司还对模拟-数字边界系统进行验证。

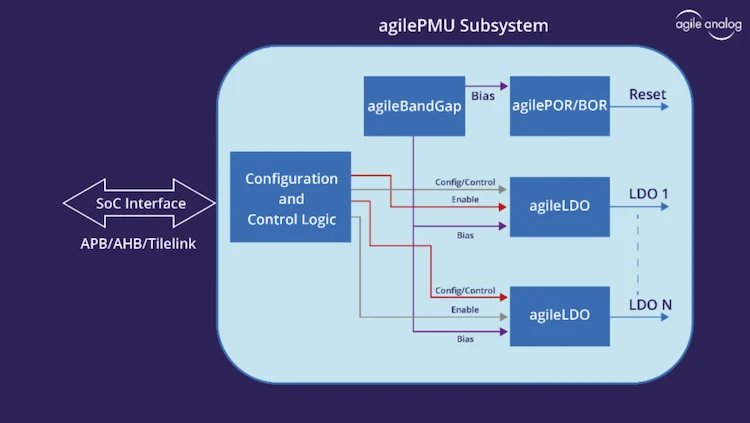

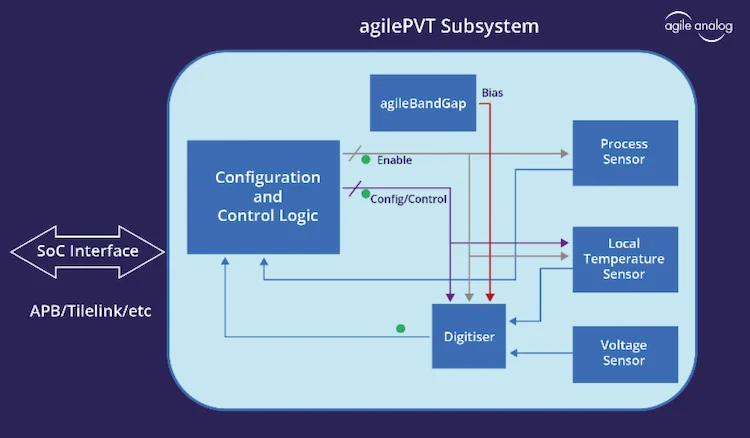

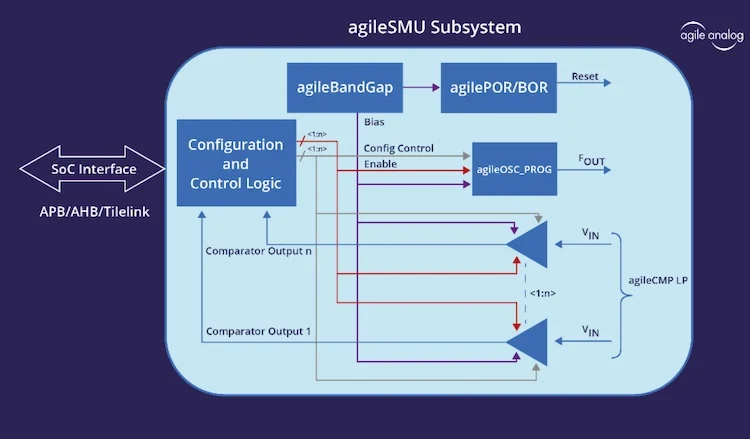

在Agile Analog最近的公告中,该公司引入了三个子系统:用于电源管理的agilePMU、用于PVT传感器的agilePVT和用于睡眠管理的Agile SMU。

AgilePMU公司

agilePMU是SoC(片上系统)和ASIC(专用集成电路)的电源管理单元,具有上电复位功能、多个低压差调节器、参考发生器、集成数字控制器和状态监测电路。

滚动以继续内容

敏捷PMU

根据Agile Analog的说法,该子系统提供了非常高的效率并优化了灵活性。数字控制器允许对每个LDO的启动和关闭、电源顺序和可编程输出电压进行精确控制。状态监视器提供有关子系统状态的实时信息。

敏捷虚拟测试

PVT传感器子系统监测设备的环境和电气特性。它包含低功率过程、电压和温度传感器、参考发生器、集成数字控制器和状态监视器。

敏捷PVT

AgileSMU公司

agileSMU是一个低功率子系统,用于管理SoC的睡眠和唤醒模式。它由用于低频SoC操作的可编程振荡器、RTC、用于启动唤醒序列的低功率比较器和上电复位组成。它还有一个集成的数字控制器和状态监视器,类似于其他两个子系统。

一镀金SMU

所有图片均由Agile Analog提供