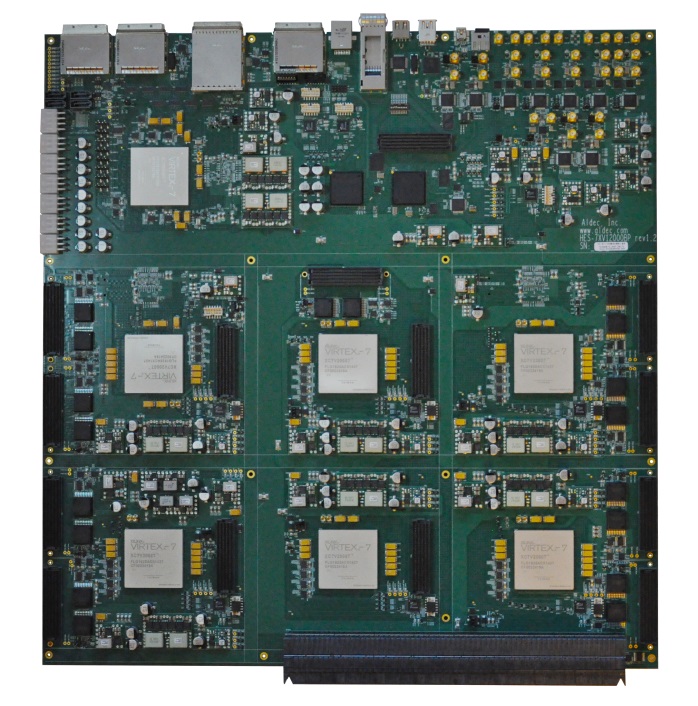

HES7XV12000BP–SoC/ASIC原型和仿真

HES7XV12000BP是一款面向SoC/ASIC硬件验证和软件验证团队的基于FPGA的大容量原型设计和仿真板。每个HES7XV12000BP板包含六个Xilinx庐 Virtex公司庐-7个2000T FPGA,具有高达7200万个ASIC门的容量,估计占FPGA利用率的60%,可扩展至288M个ASIC门。六个Virtex-7 FPGA模块中的两个连接到四个DDR3 SO-DIMM插槽,支持高达32GB的聚合内存。一个非常精确设计的时钟块提供5条全局时钟线,路由到每个FPGA设备。由于集成了不同的振荡器、可编程时钟合成器和交叉点开关复用器,它提供了多种配置选项。HES-7验证解决方案的架构旨在通过非专有背板以机架形式提供方便的实施和扩展,以实现灵活、可扩展的硬件配置。

- 零件编号:HES-7型

- 设备购买:点击在这里联系客服获取相关信息!

HES7XV12000BP是一款面向SoC/ASIC硬件验证和软件验证团队的基于FPGA的大容量原型设计和仿真板。每个HES7XV12000BP板包含六个Xilinx®Virtex®-7 2000T FPGA,具有高达7200万个ASIC门的容量,估计可用于FPGA利用率的60%,可扩展至288M个ASIC门。六个Virtex-7 FPGA模块中的两个连接到四个DDR3 SO-DIMM插槽,支持高达32GB的聚合内存。一个非常精确设计的时钟块提供5条全局时钟线,路由到每个FPGA设备。由于集成了不同的振荡器、可编程时钟合成器和交叉点开关复用器,它提供了多种配置选项。HES-7验证解决方案的架构旨在通过非专有背板以机架形式提供方便的实施和扩展,以实现灵活、可扩展的硬件配置。

主要功能和优点

- 与Aldec高性能模拟器Active HDL或Riviera PRO的成本效益捆绑包

- 卓越的品质得到业界领先的1年保修支持

- 用于背板配置的机架外形尺寸机箱

- 用于加速和仿真验证模式的原型硬件重用

- 4个SATA

- 2个PCIe x8第3代

- USB 3.0接口

- 质量保证计划+

- 千兆以太网

- BPX-非专有背板和子卡连接器

- FMC子卡连接器

- 5x全局、低偏斜、时钟线和可配置时钟块

- 4个DDR3 SO-DIMM,最高32 GB

- 1x Virtex-7 XC7VX690T主机FPGA

- 6x Virtex-7 XC7V2000T主FPGA

包装物件清单 (含配件)

- 诊断测试套件

- 用于板配置和管理的HES Proto AXI软件

- HES-7-12000板,带6个Xilinx®Virtex®-7个2000T FPGA

- 可选HES-DVM软件,用于启用仿真和仿真加速

- 可选Proto-AXI接口,高速PCIe到AMBA AXI桥接

- 板接口参考设计